# DIGITAL

K. F. CATHEY R. D. MITCHELL R. W. TINNELL

D. A. YEAGER

DELMAR PUBLISHERS, MOUNTAINVIEW AVENUE, ALBANY, NEW YORK 12205 A DIVISION OF LITTON EDUCATIONAL PUBLISHING, INC.

#### DELMAR PUBLISHERS

Division of Litton Educational Publishing, Inc. Copyright © 1972

By Technical Education Research Centers, Inc.

Copyright is claimed until Sept. 1, 1977. Thereafter all portions of this work covered by this copyright will be in the public domain.

All rights reserved. No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means – graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems – without written permission of Technical Education Research Centers.

> Library of Congress Catalog Card Number: 70-170793

#### PRINTED IN THE UNITED STATES OF AMERICA

Published simultaneously in Canada by Delmar Publishers, a division of Van Nostrand Reinhold, Ltd.

The project presented or reported herein was performed pursuant to a grant from the U.S. Office of Education, Department of Health, Education, and Welfare. The opinions expressed herein, however, do not necessarily reflect the position or policy of the U.S. Office of Education, and no official endorsement by the U.S. Office of Education should be inferred. The marriage of electronics and technology is creating new demands for technical personnel in today's industries. New occupations have emerged with combination skill requirements well beyond the capability of many technical specialists. Increasingly, technicians who work with systems and devices of many kinds – mechanical, hydraulic, pneumatic, thermal, and optical – must be competent also in electronics. This need for combination skills is especially significant for the youngster who is preparing for a career in industrial technology.

This manual is one of a series of closely related publications designed for students who want the broadest possible introduction to technical occupations. The most effective use of these manuals is as combination textbooklaboratory guides for a full-time, post-secondary school study program that provides parallel and concurrent courses in electronics, mechanics, physics, mathematics, technical writing, and electromechanical applications.

A unique feature of the manuals in this series is the close correlation of technical laboratory study with mathematics and physics concepts. Each topic is studied by use of practical examples using modern industrial applications. The reinforcement obtained from multiple applications of the concepts has been shown to be extremely effective, especially for students with widely diverse educational backgrounds. Experience has shown that typical junior college or technical school students can make satisfactory progress in a well-coordinated program using these manuals as the primary instructional material.

School administrators will be interested in the potential of these manuals to support a common first-year core of studies for two-year programs in such fields as: instrumentation, automation, mechanical design, or quality assurance. This form of *technical core* program has the advantage of reducing instructional costs without the corresponding decrease in holding power so frequently found in general core programs.

This manual, along with the others in the series, is the result of six years of research and development by the *Technical Education Research Centers*, *Inc.*, (TERC), a national nonprofit, public service corporation with headquarters in Cambridge, Massachusetts. It has undergone a number of revisions as a direct result of experience gained with students in technical schools and community colleges throughout the country.

Maurice W. Roney

# The Electromechanical Series

TERC is engaged in an on-going educational program in *Electromechani*cal Technology. The following titles have been developed for this program:

#### INTRODUCTORY

ELECTROMECHANISMS/MOTOR CONTROLS ELECTROMECHANISMS/DEVICES ELECTRONICS/AMPLIFIERS ELECTRONICS/ELECTRICITY MECHANISMS/DRIVES MECHANISMS/LINKAGES UNIFIED PHYSICS/FLUIDS UNIFIED PHYSICS/OPTICS

#### ADVANCED

ELECTROMECHANISMS/AUTOMATIC CONTROLS ELECTROMECHANISMS/SERVOMECHANISMS ELECTROMECHANISMS/FABRICATION ELECTROMECHANISMS/TRANSDUCERS ELECTRONICS/COMMUNICATIONS ELECTRONICS/DIGITAL MECHANISMS/MACHINES MECHANISMS/MATERIALS

For further information regarding the EMT program or for assistance in its implementation, contact:

Technical Education Research Centers, Inc. 44 Brattle Street Cambridge, Massachusetts 02138 Technology, by its very nature, is a laboratory-oriented activity. As such, the laboratory portion of any technology program is vitally important. *Electronics/Digital* is intended to provide meaningful experience in digital circuit analysis for students of modern technology.

The topics included provide exposure to: basic principles of digital logic, logic gates, flip-flops and other circuits, as well as to basic digital systems.

The sequence of presentation chosen is by no means inflexible. It is expected that individual instructors may choose to use the materials in other than the given sequence.

The particular topics chosen for inclusion in this volume were selected primarily for convenience and economy of materials. Some instructors may wish to omit some of the exercises or to supplement some of them to better meet their local needs.

The materials are presented in an action oriented format combining many of the features normally found in a textbook with those usually associated with laboratory manual. Each experiment contains:

- 1. An INTRODUCTION which identifies the topic to be examined and often includes a rationale for doing the exercise.

- 2. A DISCUSSION which presents the background, theory, or techniques needed to carry out the exercise.

- 3. A MATERIALS list which identifies all of the items needed in the laboratory experiment. (Items usually supplied by the student such as pencil and paper are not normally included in the lists.)

- 4. A PROCEDURE which presents step-by-step instructions for performing the experiment. In most instances the measurements are done before calculations so that all of the students can at least finish making the measurements before the laboratory period ends.

- 5. An ANALYSIS GUIDE which offers suggestions as to how the student might approach interpretation of the data in order to draw conclusions from it.

- 6. PROBLEMS are included for the purpose of reviewing and reinforcing the points covered in the exercise. The problems may be of the numerical solution type or simply questions about the exercise.

Students should be encouraged to study the text material, perform the experiment, work the review problems, and submit a technical report on each topic. Following this pattern, the student can acquire an understanding of, and skill with, basic digital circuits that will be extremely valuable on the job.

These materials on digital electronics comprise one of a series of volumes prepared for technical students by the TERC EMT staff at Oklahoma State University, under the direction of D.S. Phillips and R.W. Tinnell. The principal authors of these materials were K.F. Cathey, R.D. Mitchell, R.W. Tinnell and D.A. Yeager.

An *Instructor's Data Guide* is available for use with this volume. Mr. Kenneth F. Cathey was responsible for testing the materials and compiling the instructor's data book for them. Other members of the TERC staff made valuable contributions in the form of criticisms, corrections, and suggestions.

It is sincerely hoped that this volume as well as the other volumes in this series, the instructor's data books, and the other supplementary materials will make the study of technology interesting and rewarding for both students and teachers.

THE TERC EMT STAFF

| experiment 00001 |

|------------------|

| experiment 00010 |

| experiment 00011 |

| experiment 00100 |

| experiment 00101 |

| experiment 00110 |

| experiment 00111 |

| experiment 01000 |

| experiment 01001 |

| experiment 01010 |

| experiment 01011 |

| experiment 01100 |

| experiment 01101 |

| experiment 01110 |

| experiment 01111 |

| experiment 10000 |

| experiment 10001 |

| experiment 10010 |

| experiment 10011 |

| experiment 10100 |

| experiment 10101 |

| experiment 10110 |

| experiment 10111 |

| experiment 11000 |

| experiment 11001 |

| experiment 11010 |

| experiment 11011 |

| experiment 11100 |

| experiment 11101 |

| experiment 11110 |

|   | BINARY NUMBER SYSTEM                          | . 1   |

|---|-----------------------------------------------|-------|

| ) | BOOLEAN ALGEBRA                               | . 9   |

|   | OSCILLOSCOPE WAVEFORM MEASUREMENTS            | . 19  |

| ) | BASIC WAVEFORMS                               | . 26  |

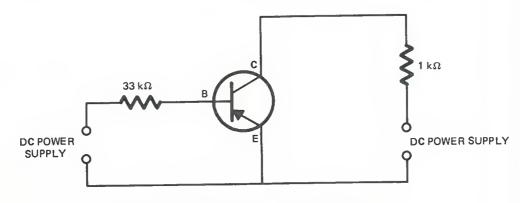

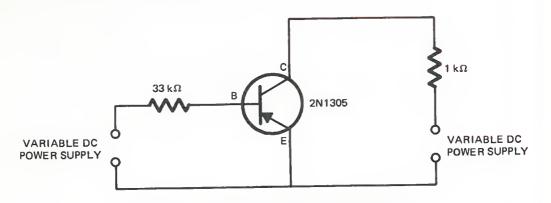

|   | TRANSISTOR SWITCHING                          | . 37  |

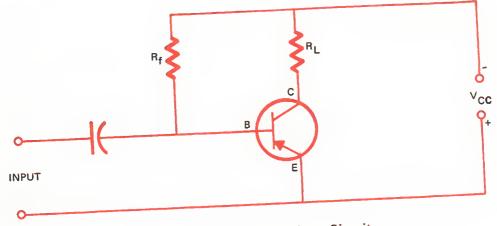

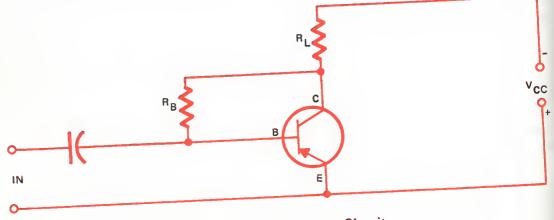

| ) | DESIGN OF THE TRANSISTOR SWITCH               | . 47  |

|   | DIODE CLIPPERS                                | . 59  |

|   | TRANSISTOR CLIPPERS AND CLAMPS                | . 67  |

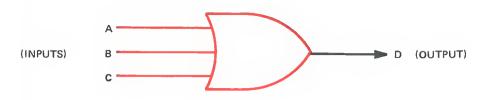

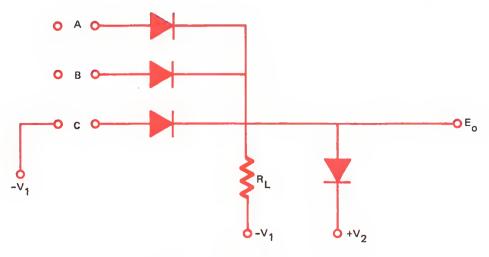

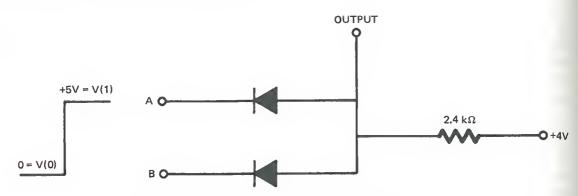

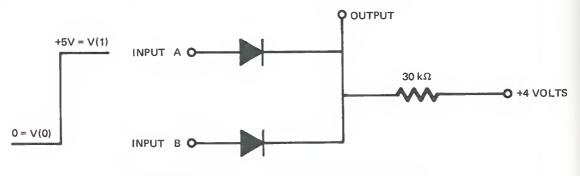

|   | DIODE LOGIC GATES                             | . 76  |

|   | RESISTOR-TRANSISTOR LOGIC (RTL) CIRCUITS      | . 85  |

|   | DIRECT COUPLED TRANSISTOR LOGIC (DCTL) GATES  | . 95  |

|   | INHIBITORS                                    | . 106 |

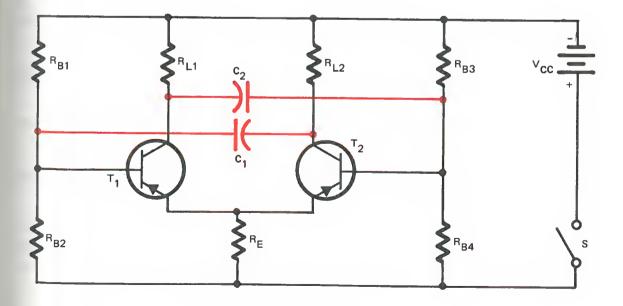

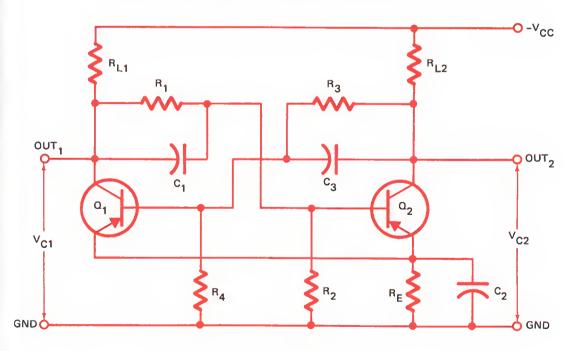

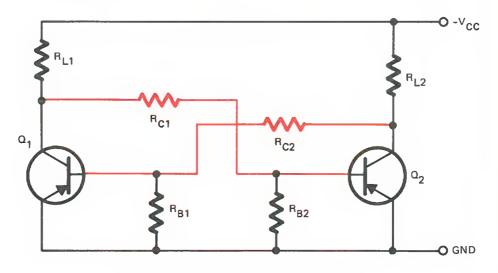

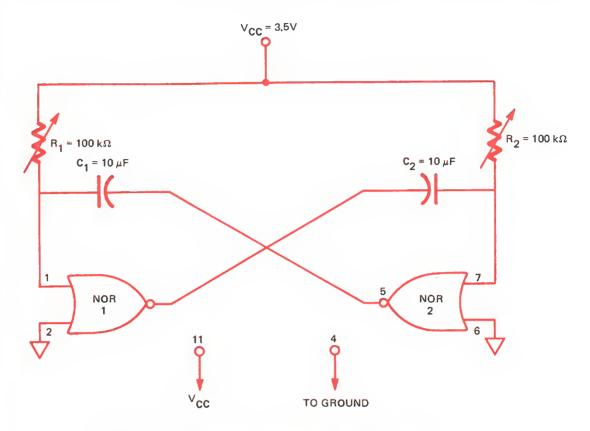

|   | FUNDAMENTALS OF MULTIVIBRATORS                | 115   |

|   | BISTABLE MULTIVIBRATORS                       | 121   |

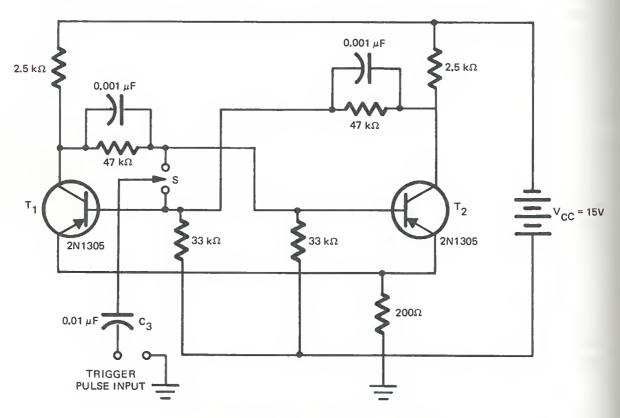

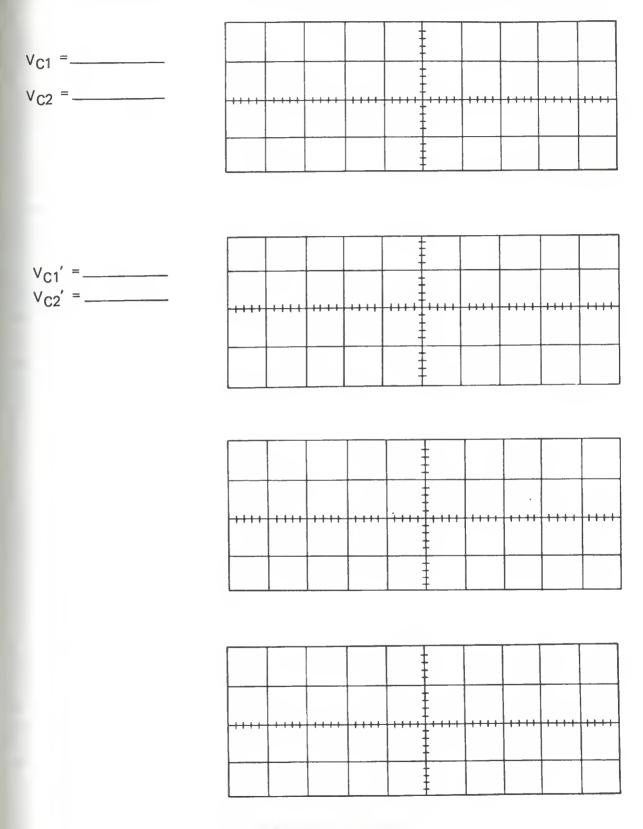

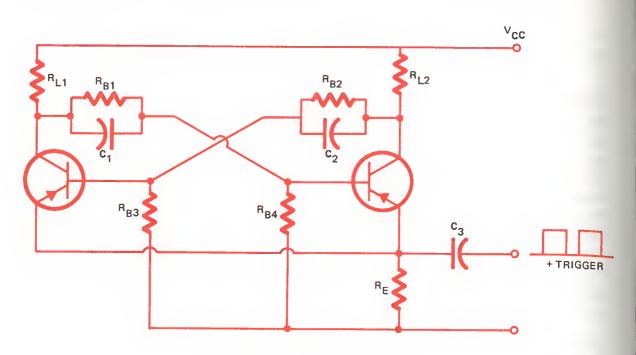

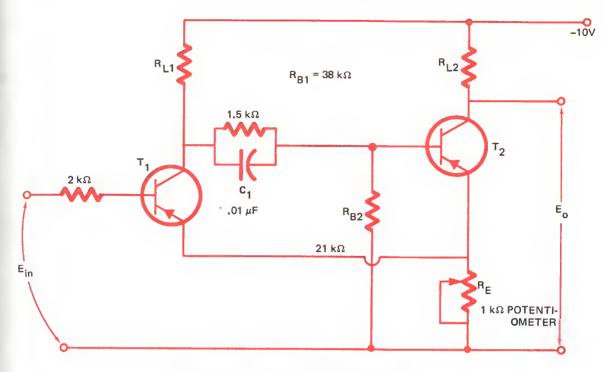

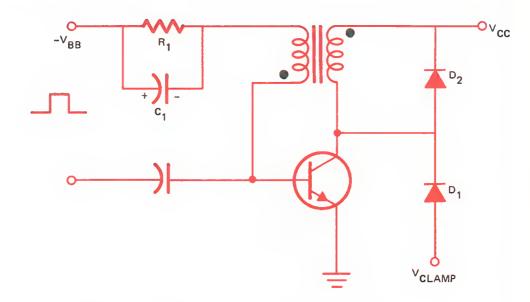

|   | MULTIVIBRATOR TRIGGER CIRCUITS                | 127   |

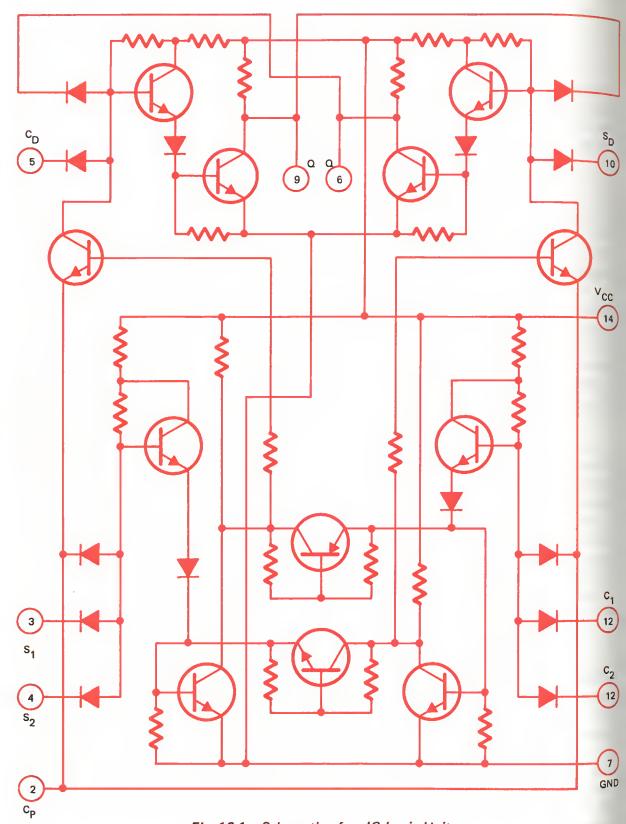

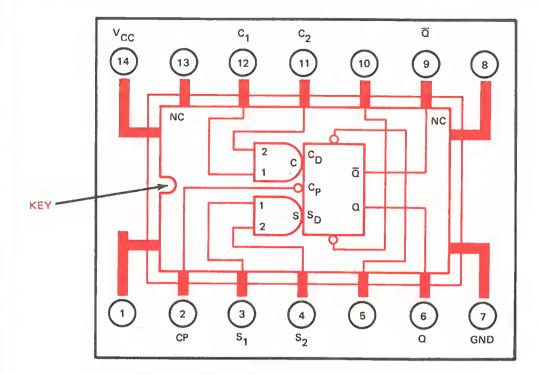

|   | INTEGRATED CIRCUIT LOGICAL FLIP-FLOPS         | 133   |

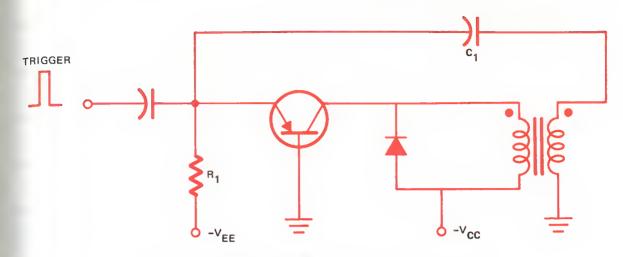

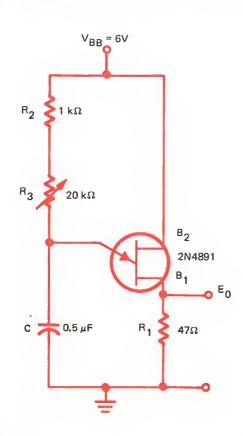

|   | BLOCKING OSCILLATORS                          | 140   |

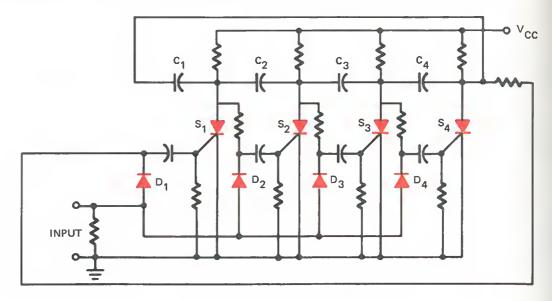

|   | TWO-DIODE STORAGE COUNTER                     | 148   |

|   | BASIC COUNTERS                                | 156   |

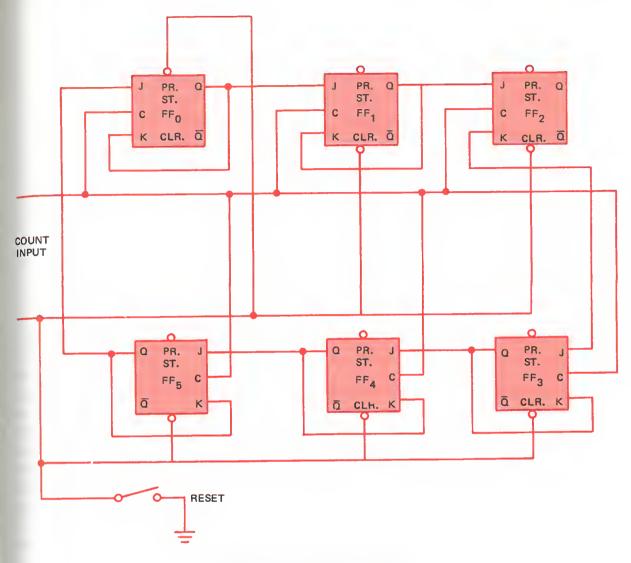

|   | RING COUNTER                                  | 165   |

|   | SHIFT REGISTERS                               | 172   |

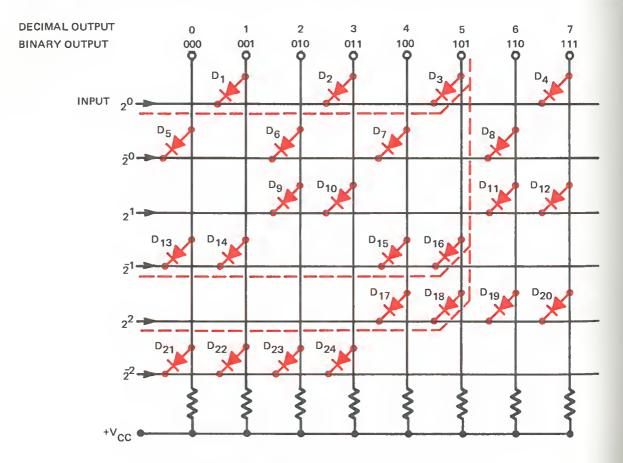

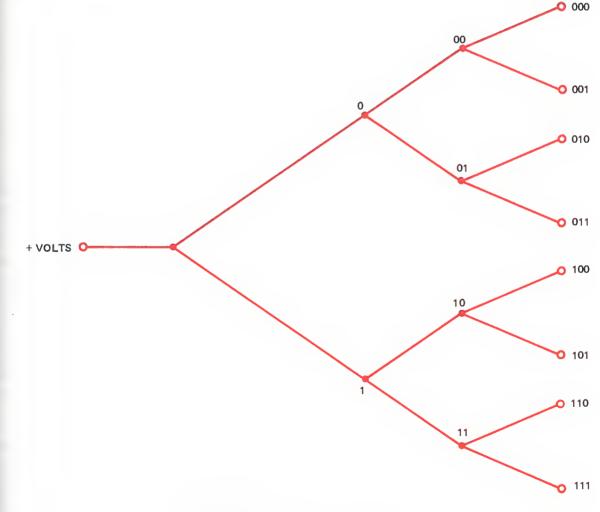

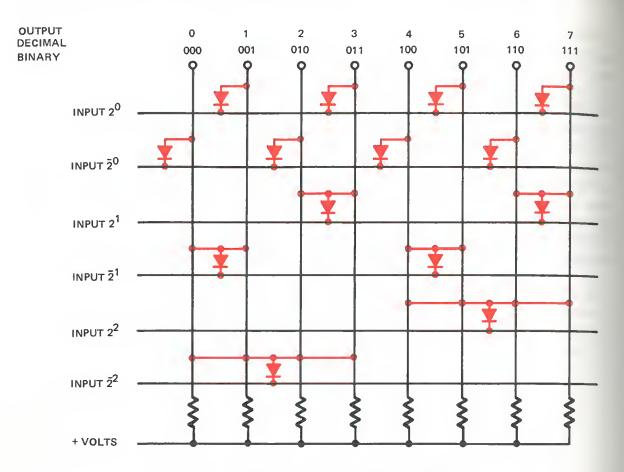

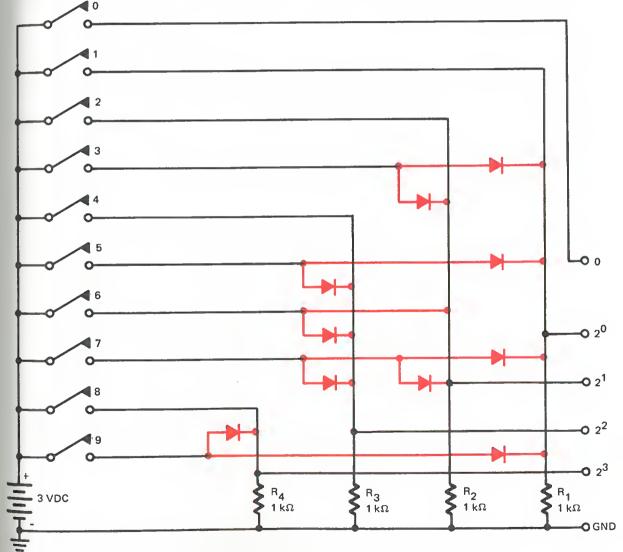

|   | DIODE MATRIX CIRCUITS                         | 184   |

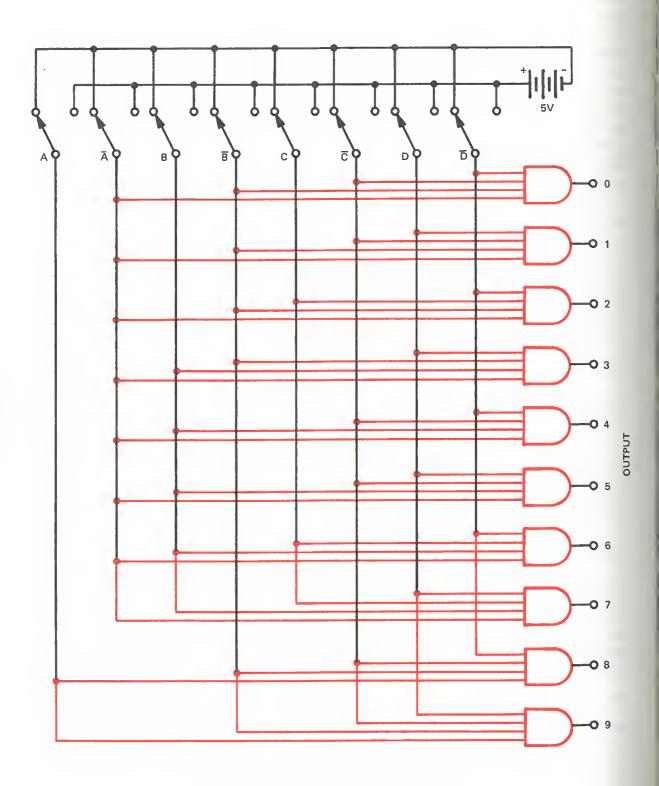

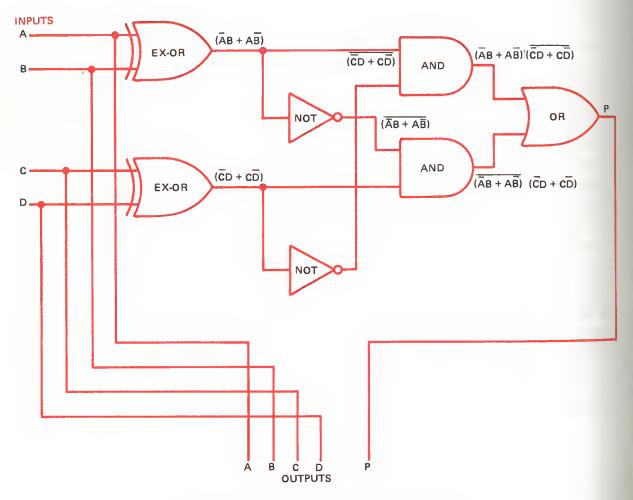

|   | PARITY CHECKING CIRCUITS                      | 192   |

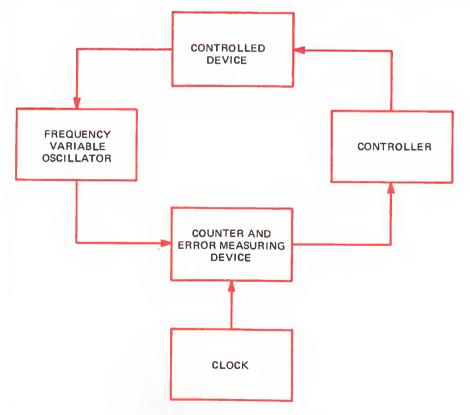

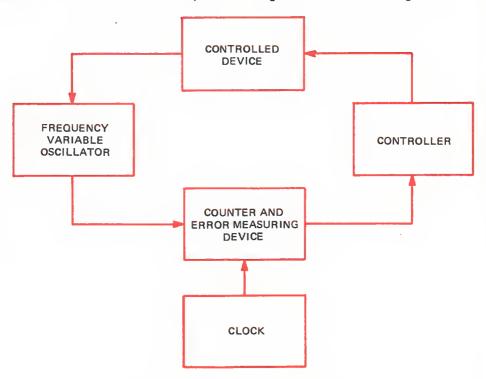

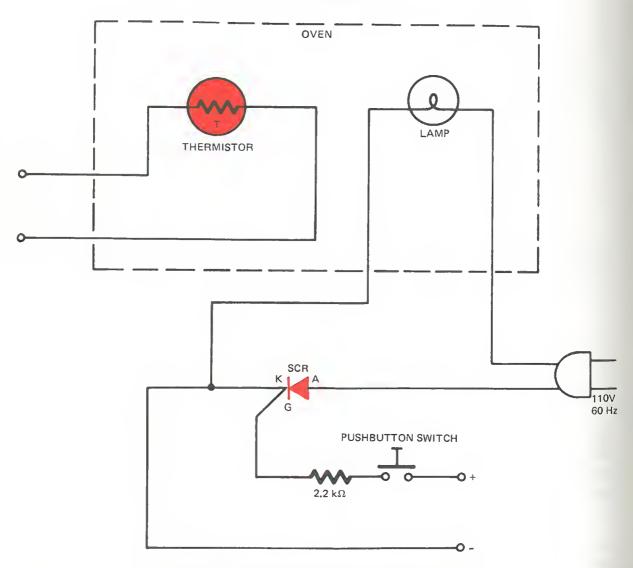

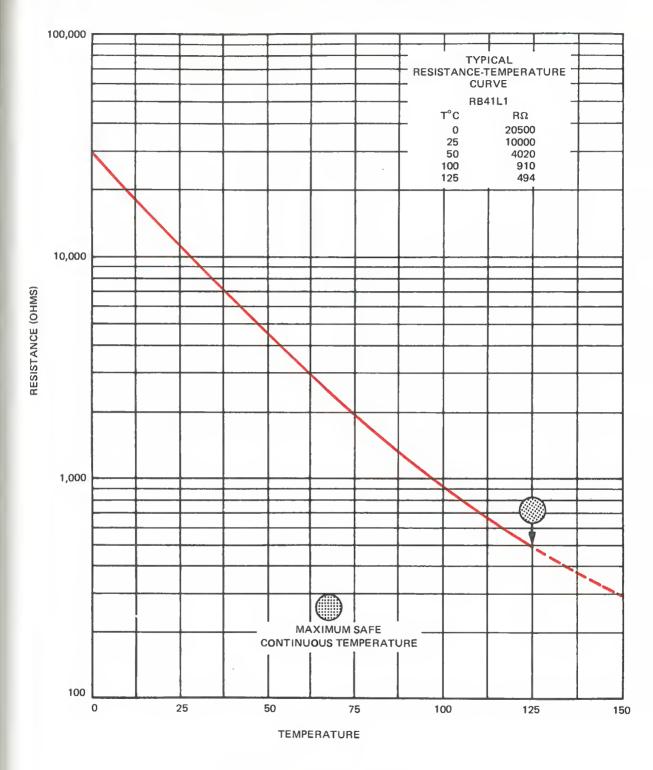

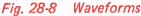

|   | INTRODUCTION TO DIGITAL TEMPERATURE CONTROL . | 199   |

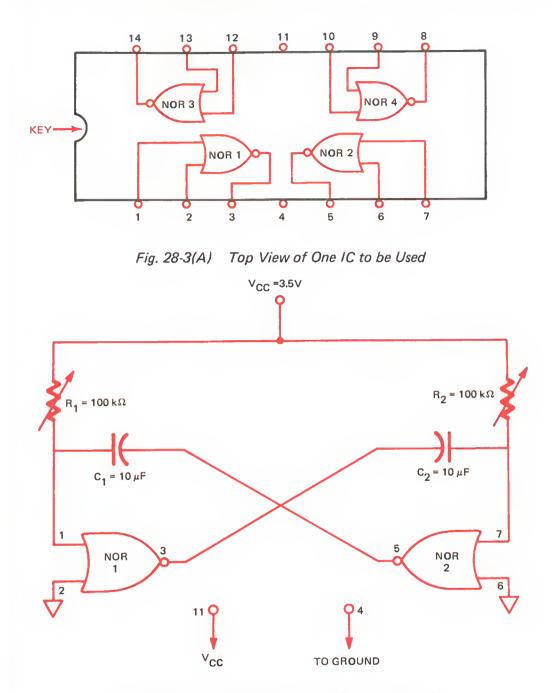

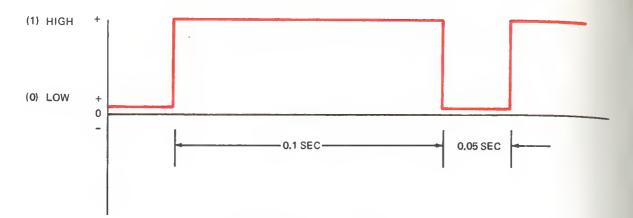

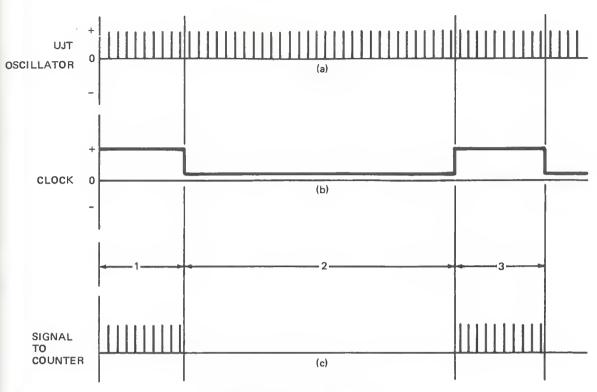

|   | TEMPERATURE CONTROL CLOCK                     | 203   |

|   | MANUAL TEMPERATURE CONTROL                    | 210   |

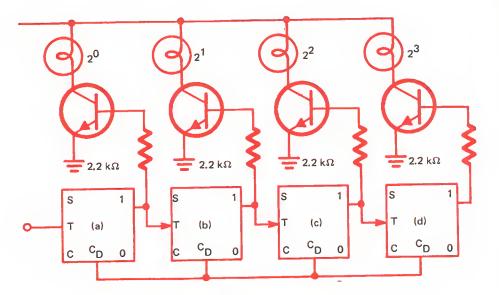

|   | TEMPERATURE CONTROL COUNTERS                  | 215   |

|   | AUTOMATIC TEMPERATURE CONTROL                 | 221   |

|   | COMPUTER PROBLEM SOLUTIONS                    | 230   |

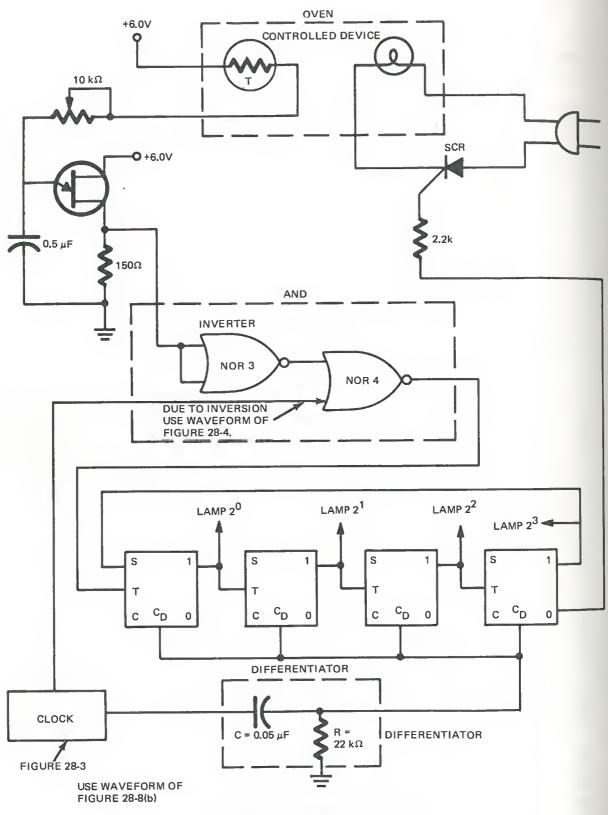

|   | SUMMARY OF LOGIC OPERATIONS                   | 233   |

|   |                                               |       |

The author and editorial staff at Delmar Publishers are interested in continually improving the quality of this instructional material. The reader is invited to submit constructive criticism and questions. Responses will be reviewed jointly by the author and source editor. Send comments to:

> Editor-in-Chief Box 5087 Albany, New York 12205

INTRODUCTION. In order to facilitate high-speed calculations in digital computers, new machine languages can be used. In this experiment we will examine the Binary Number System and perform some arithmetic operations using this system of numbers.

DISCUSSION. Binary arithmetic is the "machine language" of many computers. Α good knowledge of computer fundamentals can open many rewarding career opportunities. A digital computer can operate at very high speeds. It uses basically only two conditions, "off" and "on". These two conditions can be translated to the characters 0 and 1, which are the two digits of the Binary Number System. The computer works with these two binary numbers, and all information to be used inside the machine must be converted into binary numbers. You will need to know this machine language to understand computer operations.

Since the machines we are discussing are made up of devices that respond to only two states, we need to develop a number system to match. That is to say, our usual number system will not work with such a machine because it employs ten digits.

We all know that our everyday number system has only ten digits and that all other numbers in the system are made up of combinations of these digits. We don't usually think of 465 as being made up of four hundreds (10 times 10), six tens (10 times 1), and five units (10 times 0.1). The number 10 is called the base of the decimal system. It is NOT a basic digit in the system. In this system (or any worthwhile number system), a number is said to have position. This makes 071 mean zero hundreds, seven tens and one unit, while 710 means seven hundreds, one ten, and zero units. The position of the digits determines the magnitude of the number

The number 524 can be read five hundreds, two tens, and four units. It could also be expressed:

$$524 = 5 \times 10^2 + 2 \times 10^1 + 4 \times 10^0$$

$$(10^0 = 1)$$

(1.1)

So

$$524 = 5 \times 100 + 2 \times 10 + 4 \times 1$$

$524 = 500 + 20 + 4$

$524 = 524$

The base of the number system is the number which, when raised to the zeroth power gives the lowest position value, and when raised to the first power, it is the second position, etc. We can write the general equation for any number system as:

$$N = R^{n}d_{n} + \dots + R^{3}d_{3} + R^{2}d_{2}$$

$$+ R^{1}d_{1} + R^{0}d_{0} \qquad (1.2)$$

where:

N = the number

$$d_n$$

= the digit in that position

R = the *radix* (base of the system)

Substituting:

$$5654 = 5 \times 10^{3} + 6 \times 10^{2} + 5 \times 10^{1} + 4 \times 10^{0}$$

$$5654 = 5000 + 600 + 50 + 4$$

$$5654 = 5654$$

So much for the number system we are familiar with. It can be difficult and timeconsuming for a computer to handle a tendigit number system in its millions of computations due to its ability to add many numbers with fewer digits. For this reason the Binary Number System is often employed.

The binary system has only two digits, 0 and 1. Let's test the binary (base 2) system against our general equation to see if it produces different numbers in each position.  $2^0 = 1$  and  $2^1 = 2$ , etc., which satisfies the definition. Why couldn't the base be 0? Again, applying the rule we can see that a base 0 system probably isn't very useful because  $0^0 = 1$  and  $0^1 = 0$  as does 0 to any power. The base 1 system is similar to a base zero system. It has only one digit since multiplying one by itself any number of times produces only one. Thus, this system too is not very useful. Consequently the binary (base 2) system is the simplest usable system. It contains only two digits but can express any number with these diaits.

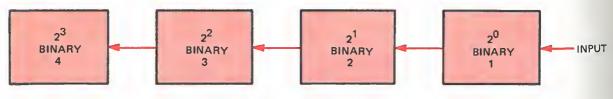

A comparison of the base 2 and base 10 systems (see Fig. 1-1) may be helpful.

The binary system has only two digits and all numbers are constructed with them. The general definition (1.2) applies to the system and can be simplified to

$$N = \dots + 8d_3 + 4d_2 + 2d_1 + 1d_0 \quad (1.3)$$

The digits in this equation

$$(d_0, d_1, d_2, d_3)$$

are either 0 or 1. If

N = 11011 in binary then N = 1  $\times$  16 + 1  $\times$  8 + 0  $\times$  4 + 1  $\times$  2 + 1  $\times$  1 N = 16 + 8 + 0 + 2 + 1 N = 27 in decimal or,

$N = 1 \times 2^{4} + 1 \times 2^{3} + 0 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}$   $N = 1 \times 16 + 1 \times 8 + 0 \times 4 + 1 \times 2 + 1$  N = 16 + 8 + 0 + 2 + 1N = 27

For instructional purposes these numbers have been expressed in the familiar decimal system. We can convert to binary notation in order to take advantage of the simpler digits.

Figure 1-2 shows the decimal digits expressed in binary code.

From equation 1.3 for the base two number system, we have evolved

$N = 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$

which is the decimal number 27 expressed in the binary form. By further inspection the binary form of the number 27 can be reached. You will notice that each of the multipliers for the powered numbers in the equation are either 0 or 1. These digits tell whether or not the particular position is filled in the binary

| Base 10                       | Base 2                       |

|-------------------------------|------------------------------|

| 10 <sup>0</sup> = 1 Units     | 2 <sup>0</sup> = 1 Units     |

| 10 <sup>1</sup> = 10 Tens     | 2 <sup>1</sup> = 2 Twos      |

| $10^2 = 100$ Hundreds         | $2^2 = 4$ Fours              |

| $10^3 = 1000$ Thousands       | $2^3 = 8$ Eights             |

| $10^4 = 10,000$ Ten Thousands | 2 <sup>4</sup> = 16 Sixteens |

Fig. 1-1 Base Ten – Base Two Comparison

2

| Decimal | Binary                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------|

| 0       | 0                                                                                                                     |

| 1       | 1 (1 × 2 <sup>0</sup> )                                                                                               |

| 2       | $10(1 \times 2^1 + 0 \times 2^0)$                                                                                     |

| 3       | $11 (1 \times 2^1 + 1 \times 2^0)$                                                                                    |

| 4       | $100 (1 \times 2^2 + 0 \times 2^1 + 0 \times 2^0)$                                                                    |

| 5       | $101 (1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0)$                                                                    |

| 6       | $110(1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0)$                                                                     |

| 7       | 111 $(1 \times 2^2 + 1 \times 2^1 + 1 \times 2^0)$                                                                    |

| 8       | $1000 (1 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 0 \times 2^0)$                                                    |

| 9       | 1001 (1 $\times$ 2 <sup>3</sup> + 0 $\times$ 2 <sup>2</sup> + 0 $\times$ 2 <sup>1</sup> + 1 $\times$ 2 <sup>0</sup> ) |

Fig. 1-2 Decimal Digits Expressed in Binary

system. In other words, when the ones appear it says, "Yes, this position is filled for this number." Therefore, the binary notation for the decimal number 27 is 11011. It has 1 power  $2^4$ , plus 1 power  $2^3$ , plus 0 power  $2^2$ plus 1 power  $2^1$ , plus 1 power  $2^0$  or "yes, yes, no, yes, yes." This corresponds well with the "on", "off" capability of devices from which computers are made.

We can get decimal numbers from binary numbers but how do we get binary numbers from decimal numbers? The procedure is quite easy and takes longer to explain than to learn. It consists of successive divisions by the base number. The base will *either* go into the number evenly, *or* have a remainder of one. The presence of the remainder determines whether or not that power position is filled. For instance, if we desire to write the binary form of  $(25)_{10}$  (which is read as twenty-five, base 10), first divide the number by two:

Remainder

| 25 divide   | d by 2 = 12 + 1                            |  |

|-------------|--------------------------------------------|--|

| Then divide | 12  by  2 = 6 + 0                          |  |

| Then divide | 6 by 2 = 3 + 0                             |  |

| Then divide | 3  by  2 = 3 + 0<br>3  by  2 = 1 + 1  Read |  |

| Then divide | 1  by  2 = 0 + 1  Up                       |  |

Listing the remainders from *bottom* to *top*, left to right we have 11001; the binary form of  $(25)_{10}$  is  $(11001)_2$ .

Conversion of the decimal system to any number system requires only division by the base of that number system, keeping track of the remainders, and reading the answer from the last remainder to the first.

Now we can change numbers back and forth at will. But what about fractional numbers? They aren't too bad if we remember that negative powers work in much the same way as positive powers. Let's go back to the general equation for base 10 and use negative exponents.

$$N = d_1 \times R^{-1} + d_2 \times R^{-2} + d_3 \times R^{-3}$$

$$+ \ldots + d_n \times R^{-n}$$

For binary, we have

$$N = d_1 \times 2^{-1} + d_2 \times 2^{-2} + d_3 \times 2^{-3}$$

ELECTRONICS/DIGITAL

Then, if we pick a fractional number 0.621, we can write the decimal form

$$0.621 = 6 \times 10^{-1} + 2 \times 10^{-2} + 1 \times 10^{-3}$$

$0.621 = 0.6 + 0.02 + 0.001$

$0.621 = 0.621$

Similarly, a fractional binary number (0.1001)<sub>2</sub> may be written as

$$(0.1001)_2 = 1 \times 2^{-1} + 0 \times 2^{-2} + 0 \times 2^{-3}$$

+ 1 × 2^{-4}

or

$$(0.1001)_{2} = 1 \times \frac{1}{2^{1}} + 0 \times \frac{1}{2^{2}} + 0 \times \frac{1}{2^{3}} + 1 \times \frac{1}{2^{4}}$$

$$(0.1001)_2 = 1 \times \frac{1}{2} + 0 \times \frac{1}{4} + 0 \times \frac{1}{8} + 1 \times \frac{1}{16}$$

$$(0.1001)_2 = 0.5 + 0 + 0 + 0.0625$$

$(0.1001)_2 = (0.5625)_{10}$

Converting fractional binary numbers to decimal numbers is an easy process.

Here is a method that can be used to convert decimal to binary. Suppose the decimal number 0.56531 is to be converted to binary.

First, multiply  $0.56531 \times 2 =$ 1.13062Then multiply  $0.13062 \times 2 =$ 0.26124Then multiply  $0.26124 \times 2 =$ 0.52248Then multiply  $0.52248 \times 2 =$ 1.04496Then multiply  $0.04496 \times 2 =$ 0.8992Etc.ReadDown

Collecting the whole numbers from the top down we read the answer as  $(0.10010...)_2$ .

This can be checked by the previous method.

$(0.10010)_2 = 1 \times 2^{-1} + 0 \times 2^{-2} + 0 \times 2^{-3}$ + 1 × 2^{-4}  $(0.10010)_2 = 0.5 + 0.0625$  $(0.10010)_2 = (0.5625)_{10}$

This process can be carried out to any number of places required. When the answer is not accurate enough, the process may be carried out to more places until the desired accuracy is achieved.

Now that we are familiar with the Binary Number System and how to get from one system to another, it is time to investigate operations in the binary system. In order to understand the computer, we must learn how it makes computations in this number system.

Binary arithmetic is concerned with the same four basic operations found in decimal arithmetic. These basic operations are addition, subtraction, multiplication, and division. We will do some of these operations with pencil and paper to illustrate how the machine does them automatically.

Binary addition has only four possible combinations. The combinations are:

- 0 + 0 = 0 (1.4)

- 1 + 0 = 1 (1.5)

- 0 + 1 = 1 (1.6)

or

$$1 + 1 = 0 + carry 1$$

(1.7)

Since 1 + 1 would be 2, the binary system requires that it be written in two places as 10. This means that the 1 must be carried to the next higher place for addition. So 1 + 1 = 10. An example might help. Take the decimal number 13, written 001101 in binary and add the decimal 37, written 100101 in binary.

110010 is the binary form of 50.

- 1 + 1 = 10, yields the first digit 0, carry the 1.

- 1 + 0 + 0 = 1, yields the second digit 1, plus nothing to carry.

- 1 + 1 = 10, yields the third digit 0, plus 1 to carry.

- 1 + 1 + 0 = 10, yields the fourth digit 0, plus 1 to carry.

- 1 + 0 + 0 = 1, yields the fifth digit 1, plus nothing to carry.

- 0 + 1 = 1, yields the sixth digit 1, plus nothing to carry.

Putting all the digits together, we get 110010.

Binary subtraction is the same operation as in decimal. The only tricky thing is zero minus one, which requires borrowing from the next higher position.

We can see that:

| 0 - 0 = 0 (1.8) |

|-----------------|

|-----------------|

1 - 1 = 0 (1.9)

1 - 0 = 1 (1.10)

But

0 - 1 = 1 + borrow (1.11)

(Because the two of the binary system is in action again, and after borrowing, 2 - 1 = 1).

$$10 = (2)_{10}$$

- 01 = (1)\_{10}

01 = (1)\_{10}

One cannot be subtracted from zero so a one must be borrowed from the next digit, making the binary 10 or  $(2)_{10}$ . Subtracting a binary

one from a binary two leaves a binary one, just as in the decimal system. To check this, add binary 1 + 1 = 0 + carry or  $10 \text{ or } (2)_{10}$ .

Let's try another example:

The binary 11011001 corresponds to  $(217)_{10}$  minus 10101011, or  $(171)_{10}$  equals 00101110 or  $(46)_{10}$ . These numbers can be verified by the technique described earlier.

There are some other methods for binary subtraction but they will not be discussed here.

The next operation to be discussed is that of binary multiplication. It is a quite simple operation. Actually, the computer performs multiplication by repeated addition. In order to examine how the system works, let's consider the following example:

| 110101    |  |

|-----------|--|

| X 111     |  |

| 110101    |  |

| 110101    |  |

| 110101    |  |

| 101110011 |  |

or  $(53)_{10} \times (7)_{10} = (371)_{10}$ .

There is an easy way to add. It consists of a few simple rules.

- Count the number of ones + carries.

A. If the resulting number is even, the sum is zero.

- B. If the resulting number is odd, the sum is one.

- 2. Count the pairs of ones to determine how many ones are to be carried to the next higher position. Be sure to count the carried ones in the pairs.

1100

Binary division is as simple as binary multiplication. Quotients other than one or zero are impossible.

110 1001000

<u>110</u> 00110

110

00000

By using your conversion, you will find that binary  $110 = (6)_{10}$ ,  $(1001000)_2 = (72)_{10}$ , and  $(1100)_2 = (12)_{10}$ . It is easy to see that if the divisor will not go into the dividend, the divisor cannot be subtracted from the dividend and leave a positive difference.

#### MATERIALS

Pencil and paper

#### PROCEDURE

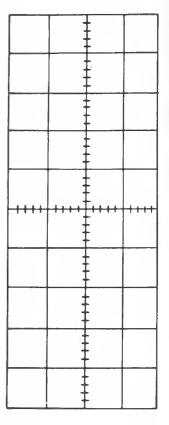

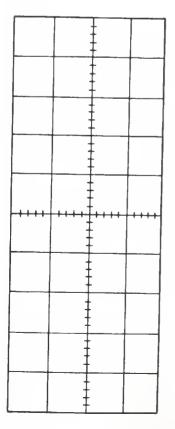

- 1. Develop the positive integers of the Binary Number System through 100 and record them in figure 1-3A.

- 2. Convert the following binary numbers to their decimal equivalents and record them in figure 1-3B.

111011101, 11101101, 10110.1101, .11011, .10001

3. Convert the following decimal numbers to binary and check by converting binary back to decimal and record in figure 1-3C.

- 4. Add the following groups of binary numbers and convert the answers. Record in figure 1-3D.

- 5. Subtract the following, convert the answers and record in figure 1-3D.

| (a) | 10110   | (b) 100110001101 |

|-----|---------|------------------|

|     | - 01010 | - 010101110010   |

6. Multiply the following binary number. Convert the multiplier and multiplicand and check your answer. Record in figure 1-3E.

7. Divide the following binary numbers. Convert the divisor and dividend. Check the answer. Record in figure 1-3E.

### 1001 1010001

ANALYSIS GUIDE. In this exercise you should develop some ideas about how the computer handles these calculations. Explain how a computer can know that the number it is trying to subtract is smaller than the number to be subtracted from? Discuss why it is useful for a computer to use the Binary Number System. Show how a computer would perform a simple multiplication problem.

| Decimal | Binary | Decimal | Binary | Decimal | Binary | Decimal | Binary |

|---------|--------|---------|--------|---------|--------|---------|--------|

| 1       |        | 26      |        | 51      |        | 76      |        |

| 2       |        | 27      |        | 52      |        | 77      |        |

| 3       |        | 28      |        | 53      |        | 78      |        |

| 4       |        | 29      |        | 54      |        | 79      |        |

| 5       |        | 30      |        | 55      |        | 80      |        |

| 6       |        | 31      |        | 56      |        | 81      |        |

| 7       |        | 32      |        | 57      |        | 82      |        |

| 8       |        | 33      |        | 58      |        | 83      |        |

| 9       |        | 34      |        | 59      |        | 84      |        |

| 10      |        | 35      |        | 60      |        | 85      |        |

| 11      |        | 36      |        | 61      |        | 86      |        |

| 12      |        | 37      |        | 62      |        | 87      |        |

| 13      |        | 38      |        | 63      |        | 88      |        |

| 14      |        | 39      |        | 64      |        | 89      |        |

| 15      |        | 40      |        | 65      |        | 90      |        |

| 16      |        | 41      |        | 66      |        | 91      |        |

| 17      |        | 42      |        | 67      |        | 92      |        |

| 18      |        | 43      |        | 68      |        | 93      |        |

| 19      |        | 44      |        | 69      |        | 94      |        |

| 20      |        | 45      |        | 70      |        | 95      |        |

| 21      |        | 46      |        | 71      |        | 96      |        |

| 22      |        | 47      |        | 72      |        | 97      |        |

| 23      |        | 48      |        | 73      |        | 98      |        |

| 24      |        | 49      |        | 74      |        | 99      |        |

| 25      |        | 50      |        | 75      |        | 100     |        |

(A)

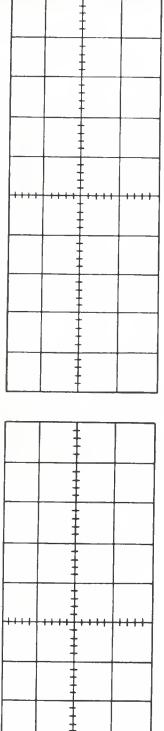

| Binary     | Decimal | Decimal | Binary |

|------------|---------|---------|--------|

| 111011101  |         | 353     |        |

| 11101101   |         | 557     |        |

| 10110.1101 |         | 632     |        |

| .11011     |         | 0.725   |        |

| .10001     |         | 0.5625  |        |

(B)

(C)

Fig. 1-3 The Data Tables

# EXPERIMENT 00001 BINARY NUMBER SYSTEM

| Binary | Decimal |

|--------|---------|

| 4.(a)  |         |

| 4.(b)  |         |

| 4.(c)  |         |

| 5.(a)  |         |

| 5.(b)  |         |

(D)

| Binary | Decimal |

|--------|---------|

| 6.     |         |

| 7.     |         |

(E)

Fig. 1-3 The Data Tables (Cont.)

#### PROBLEMS

1. What is the answer in binary numerals?

1572 - 964

2. Give the answer in decimal.

|   | 001101 |  |

|---|--------|--|

| + | 100101 |  |

3. 110101 × 111 ÷ 87 = ?

experiment

**INTRODUCTION.** When problems of logic are considered, some interesting mathematical forms can be developed for expression. Boolean algebra is one of these mathematical forms. In this experiment we will examine some of the shorthand notations of Boolean algebra and learn a few Boolean theorems.

00010

**DISCUSSION.** Some of the principles of logic are quite old. Many were first set forth by Aristotle. He said that there existed certain statements that were either true or false and never partly true or false. In 1847, George Boole, an English mathematician, developed a shorthand notation for these statements.

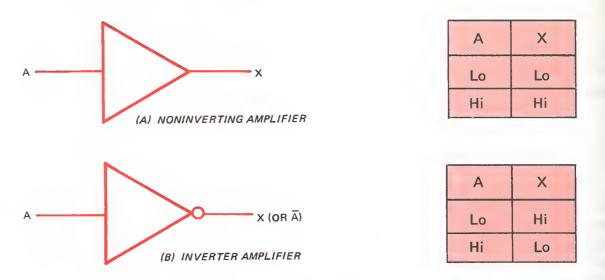

Boolean algebra employs operations with single value functions having two possible discrete states.

For our purposes, Boolean algebra applies to the binary digits of 0 and 1. When applied to a simple switch, the two values can correspond to "open" and "closed". For convention, the open state is usually labelled 0 and the closed state, 1. Boolean algebra is similar to ordinary algebra and arithmetic. The distributive law applies and factoring and expansion are permitted. It is different in that it is a mathematics in which variables have two possible states. A statement is either true or false. The switch is either "open" or "closed," 0 or 1. What better language could be chosen for a discussion of switch circuits? Boolean algebra provides a convenient method of expressing switching arrangements without drawing the circuit. It provides a means of finding a number of circuits that will perform a given switch function.

Only two operations are permitted in logical algebra. They are addition and multiplication. The basic laws for logic addition are

| 0 + 0 = 0 | (2.1) |

|-----------|-------|

|-----------|-------|

0 + 1 = 1 (2.2)

$$1 + 0 = 1$$

(2.3)

$$1 + 1 = 1$$

(2.4)

while for logic multiplication, the laws are

| $0 \times 0 = 0$ | (2.5) |

|------------------|-------|

|------------------|-------|

$1 \times 0 = 0$  (2.6)

$$0 \times 1 = 0$$

(2.7)

$$1 \times 1 = 1$$

(2.8)

Equation 2.4 may look a little suspicious to you. Remember that it is a *law*; also remember that 1 is the maximum value in the system. What this law really says is that "all" plus "all" still equals "all", just as nothing plus nothing is still nothing.

The words AND and OR can be substituted in the laws of Boolean algebra and this helps in understanding the meanings of the laws. AND can be substituted for the multiplication sign while OR can be substituted for the addition sign. The laws then become

| 0 or 0 = 0  |

|-------------|

| 0 or 1 = 1  |

| 1 or 0 = 1  |

| 1 or 1 = 1  |

| 0 and 0 = 0 |

| 1 and 0 = 0 |

| 0 and 1 = 0 |

| 1 and 1 = 1 |

This makes the equation 1 + 1 = 1 read "1 or 1 is still 1" while  $1 \times 1 = 1$  reads "1 and 1 are also still one." This is the meaning of these laws which directly relate to AND and OR circuits in computer logic design. It should be noted here that, while the plus sign is almost universally used to denote OR, the X and the dot ( $\cdot$ ) are both occasionally used for AND.

Functions may be evaluated in the usual way. However, due to their simplicity, all the possible values may be determined. That is, a Boolean function of two variables has only four possible choices. Given two variables, A and B, we can write *all* of the possible combinations:

$$A = 0, B = 0$$

$A = 0, B = 1$

$A = 1, B = 0$

$A = 1, B = 1$

Since this is true, the Boolean function

$$f(A, B) = A + AB$$

(2.9)

can have only four possible solutions. These arise from the possible combinations given

previously and may be written as follows:

For the first combination, A = 0, B = 0The function f (A, B) = A + AB = ? Substituting f (0, 0) = 0 + (0) (0) = 0

For the combination A = 0, B = 1f(0, 1) = 0 + (1)(0) = 0

For the combination

$$A = 1$$

,  $B = 0$

f (1, 0) = 1 + (1) (0) = 1

For the combination A = 1, B = 1f (1, 1) = 1 + (1) (1) = 1

Careful inspection of the answer column for these expressions will reveal that the answer corresponds to the value substituted for A. From this fact, we can observe that:

$$A + AB = A \tag{2.10}$$

This theorem is called the law of absorption.

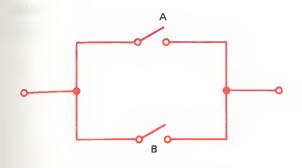

The real value of Boolean notation is that it follows the laws of many physical systems. For our purposes, it manifests itself as *switching logic*.

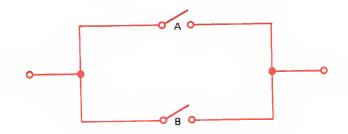

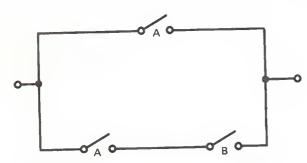

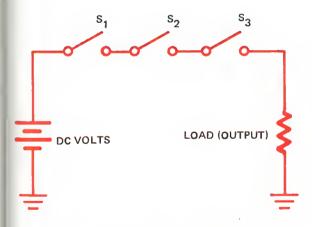

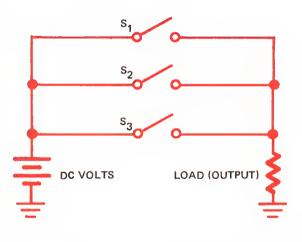

Consider the electrical systems of two switches each, figures 2-1 and 2-2. In figure 2-1 an output is possible only if both A and B are closed. In figure 2-2 an output is available

Fig. 2-1 Two Switches in Series

Fig. 2-2 Two Switches in Parallel

10

#### SERIES SWITCHES

| A      | B      | Output |

|--------|--------|--------|

| Open   | Open   | No     |

| Closed | Closed | Yes    |

| Open   | Closed | No     |

| Closed | Open   | No     |

|        |        |        |

PARALLEL SWITCHES

| A      | В      | Output |

|--------|--------|--------|

| Open   | Open   | No     |

| Closed | Closed | Yes    |

| Closed | Open   | Yes    |

| Open   | Closed | Yes    |

|        |        |        |

if either A or B is closed. The table in figure 2-3 lists all the possible combinations for both sets of switches.

Substituting 0 for open (or on) in the switching tables gives us two tables which correspond to Boolean multiplication and addition. These tables are shown in figure 2-4.

This table illustrates an important fact. Series switches can be used to represent multiplication and parallel switches can be used to represent addition. This is a very important application of Boolean algebra for us, because it can be used to describe switch or transistor logic circuits. Not only can multiplication and addition be represented by switch combinations, but switch combinations can be represented by the multiplication and

### addition operations. This opens the possibility of developing a machine which can do these mathematical operations electronically using switches or transistors.

The dual of an algebraic equation is that equation obtained from the original by interchanging certain pairs of symbols. This becomes important to us in our study of Boolean algebra in that the dual of each law is also a law, and each theorem based on the law has a dual. This saves much time. For example, the law 0 + 0 = 0 has as its dual  $1 \times 1 = 1$ , when 1 is substituted for 0 and X is substituted for +. When any theorem in Boolean algebra is proven, its dual is automatically accepted.

Many theorems can be developed for Boolean algebra. When we restrict the pos-

#### BOOLEAN MULTIPLICATION (Series Switches)

| A | В | AB |

|---|---|----|

| 0 | 0 | 0  |

| 1 | 1 | 1  |

| 0 | 1 | 0  |

| 1 | 0 | 0  |

BOOLEAN ADDITION (Parallel Switches)

| А | В | A + B |

|---|---|-------|

| 0 | 0 | 0     |

| 1 | 1 | 1     |

| 1 | 0 | 1     |

| 0 | 1 | 1     |

Fig. 2-4 Boolean Multiplication and Addition

sible number of variables to 0 and 1, a method of proof presents itself which is normally impossible in regular algebra because of the infinite number of values which may be assigned to the variables. This method of proof is called the *exhaustion method* and consists of direct substitution of all the possible combinations of 0 and 1. This can be directly related to switch circuits and the theorems can indeed be demonstrated using switch circuits. The use of theorems allows quick reduction of many complex equations to simpler forms, as well as the design of switch circuits which can perform specific switching functions.

#### **THEOREM NUMBER 1**

(a) A + A = A (A or A is A) (2.11) Its dual (b)  $A \times A = A$  (A and A are A)

To prove this we can use a *truth table* and list all of the possible combinations.

| Α | A + A = ? |  |

|---|-----------|--|

| 1 | 1 + 1 = 1 |  |

| 0 | 0 + 0 = 0 |  |

The dual theorem  $A \times A = A$  can be proven similarly, as below, but actually needs no proof since it is a dual of the addition theorem. Therefore, the proofs of the duals will not be shown after this.

| Α | $A \times A = ?$ |

|---|------------------|

| 1 | 1 X 1 = 1        |

| 0 | $0 \times 0 = 0$ |

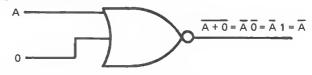

THEOREM NUMBER 2 (Identity Law)

|   | $A + 0 = A$ $A \times 1 = A$ | (2.12) |

|---|------------------------------|--------|

| А | A + 0 = ?                    |        |

| 1 | 1 + 0 = 1                    |        |

| 0 | 0 + 0 = 0                    |        |

THEOREM NUMBER 3 (Identity Law)

$$\begin{array}{c|c}

A + 1 = 1 \\

A \times 0 = 0 \\

\hline \\

1 \\

0 \\

0 + 1 = 1 \\

\end{array} (2.13)$$

THEOREM NUMBER 4 (Commutative and Associative Laws)

|   | (a)<br>(b) | $A + B = B + A$ $A \times B = B \times A$ | (2.14)    |

|---|------------|-------------------------------------------|-----------|

| А | в          | A + B = ?                                 | B + A = ? |

| 0 | 0          | 0 + 0 = 0                                 | 0 + 0 = 0 |

| 0 | 1          | 0 + 1 = 1                                 | 1 + 0 = 1 |

| 1 | 0          | 1 + 0 = 1                                 | 0 + 1 = 1 |

| 1 | 1          | 1 + 1 = 1                                 | 1 + 1 = 1 |

THEOREM NUMBER 5 (Distributive Law)

(a) (A + B) + C = A + (B + C); (2.15)  $A \times (B + C) = A \times B + A \times C$

(b)  $(A \times B) \times C = A \times (B \times C)$

| ABC | (A + B) + C = ? | A + (B + C) = ? |

|-----|-----------------|-----------------|

| 000 | 0 + 0 = 0       | 0 + 0 = 0       |

| 100 | 1+0=1           | 1 + 0 = 1       |

| 010 | 1 + 0 = 1       | 0 + 1 = 1       |

| 001 | 0 + 1 = 1       | 0 + 1 = 1       |

| 110 | 1 + 0 = 1       | 1 + 1 = 1       |

| 101 | 1 + 1 = 1       | 1 + 1 = 1       |

| 011 | 1 + 1 = 1       | 0 + 1 = 1       |

| 111 | 1 + 1 = 1       | 1 + 1 = 1       |

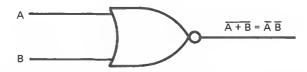

THEOREM NUMBER 6 (DeMorgan's Law)

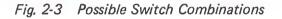

(a)  $(A + B) \times (A + C) = A + (B \times C)$

(b)  $(A \times B) + (A \times C) = A \times (B + C)$  (2.16)

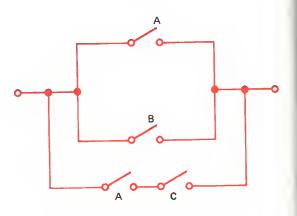

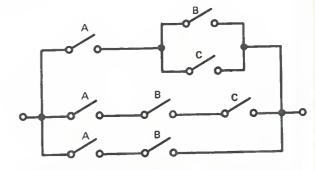

The proof is similar to the other theorems. It is interesting to examine the switch network equivalent for theorem six (a). It will

Fig. 2-5 Theorem Six

be found that the two networks are open and closed for the same conditions, and the two networks are equivalent.

THEOREM NUMBER 7 (Absorption Law) (a)  $A + (A \times B) = A$

(b)

$$A \times (A + B) = A$$

(2.17)

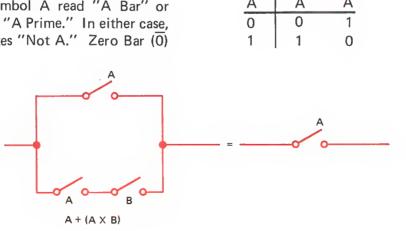

This theorem may be proven by exhaustion through a truth table. Fig. 2-6 is an electrical representation. This combination shows how difficult networks may be reduced to simple networks

Now we reach a departure from our ordinary algebra. This concept is the "not" function. The not function is usually indicated by the symbol  $\overline{A}$  read "A Bar" or the symbol A' read "A Prime." In either case, the symbol indicates "Not A." Zero Bar ( $\overline{0}$ )

indicates "not zero." Since the only other possibility we have in binary is 1, a "not zero" is equal to 1.  $\overline{1} = 0$ , or "not one" is zero. To continue this to general terms,  $\overline{A} = \text{Not } A$ . Then, if  $\overline{A} = 0$ , A = 1; or if  $\overline{A} = 1$ , A = 0.

The electrical illustration of this is a *single-pole double-throw* switch. When one set of contacts is "made," the other is "not" made. The following theorems are derived from the "not" function.

THEOREM NUMBER 8 (Double Negation)

$$(\overline{\overline{A}}) = A$$

(2.18)

Read not (not-A) = A

Fig. 2-6 Theorem Seven

Electrically, a switch that was open, but has now been returned to the closed position. illustrates this theorem.

#### **THEOREM NUMBER 9**

(a)

$$A + \bar{A} = 1$$

(2.19)

(b)  $A \times \bar{A} = 0$

A

$$A + \overline{A} = ?$$

0

$0 + 1 = 1$

1

$1 + 0 = 1$

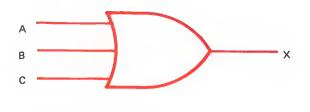

#### **THEOREM NUMBER 10**

(a)

$$(\overline{A + B + C}) = \overline{A} \cdot \overline{B} \cdot \overline{C}$$

(2.20)

(b)  $(\overline{A \times B \times C}) = \overline{A} + \overline{B} + \overline{C}$

#### **THEOREM NUMBER 11**

(a)  $A \times (\overline{A} + B) = A \times B$ (2.21)(b)  $A + (\overline{A} \times B) = A + B$

#### **THEOREM NUMBER 12**

- (a)  $(A + B) \times (\overline{A} + C) \times (B + C)$ (2.22) $= (A + B) \times (\overline{A} + C)$

- (b)  $(A \times B) + (\overline{A} \times C) + (B \times C)$  $= (A \times B) + (\overline{A} \times C)$

Now that we have seen several theorems, it is time to examine their usage. These theorems can be used to expand terms, factor and reduce complex polynomials to simpler forms. When we remember that all Boolean expressions can really be switching combinations, the real worth of the system is realized. It gives us a tool which allows understanding of highly complex switching circuits from the design standpoint, as well as providing the ability to investigate existing switching systems. A simple example of each method may help you understand this useful tool.

Example:

form

Given:

$$AB + \overline{C} + \overline{AC} + B = ?$$

Reduce this

$$\overline{AB} \times (\overline{C}) + \overline{AC} + B = ?$$

expressionTheorem 10 (a)to a simpler $(\overline{A} + \overline{B}) C + \overline{AC} + B = ?$ formTheorem 8 & 10 (b) $\overline{AC} + \overline{BC} + \overline{AC} + B = ?$ Theorem 6 (b) $\overline{AC} + (\overline{BC} + B) = ?$ Theorem 1 (a) $\overline{AC} + C + B = ?$ Theorem 11 (b) $C + B = Answer, Theorem 7 (a)*$

\*Writing the next to last step  $\overline{A} \times C + C + B = ?$  makes it look more like 7 (a).

Given the expression

1

$$A + B + AC = ?$$

draw the switch diagram.

The Example Circuit Fig. 2-7

Simplify algebraically:

| A + B + AC =  | Rearranging terms by |

|---------------|----------------------|

| A + AC + B =  | Theorem 7 (a)        |

| A + B = Answe | r                    |

Draw the network.

Fig. 2-8 The Simplified Circuit

Many more examples could be given, but these two should be enough to demonstrate the worth of the system. In the highly complex switching circuitry of a digital computer, simplifications of this sort are a great help. With a knowledge of the theorems, we can solve almost any circuit for a workable solution. You should realize that the solution arrived at may not necessarily be the only solution nor even the best. This is because the stage at which we decide to stop the mathematical manipulation is largely a matter of choice. There are no easy rules for manipulating the theorems and expressions. As in algebra, you can start by removing the parentheses (or bars), then study and compare the theorem for application.

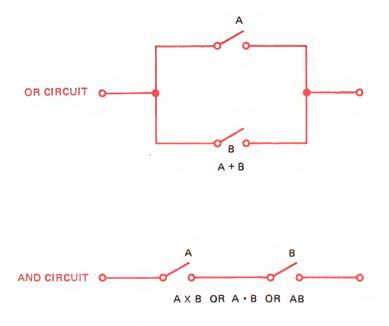

Remember, in our field OR (+) represents a parallel circuit while AND (X) represents a series circuit.

Many times in the computer field you will find a set of series switches (electronic, relay, or any other type) referred to as an AND circuit. While a set of parallel switches is referred to as an OR circuit.

#### MATERIALS

- 10 SPST switches 3 SPDT switches

- 1 VOM or FEM

- i vom or i Em

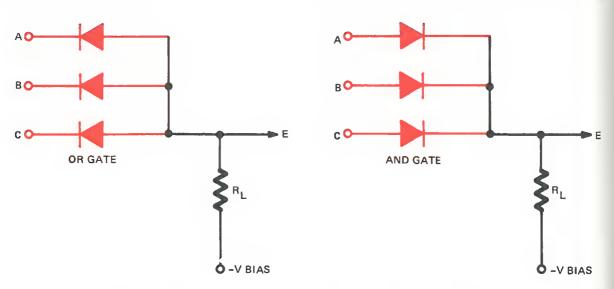

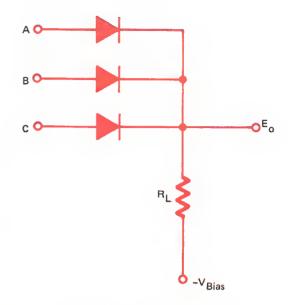

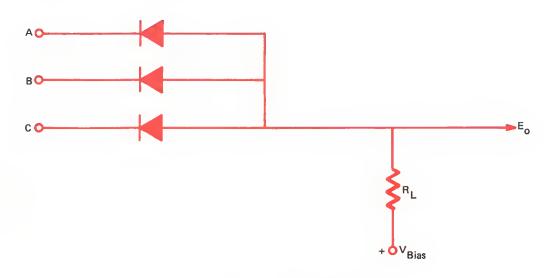

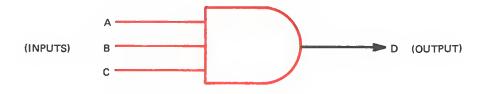

Fig. 2-9 AND – OR Switch Circuits

#### PROCEDURE

- 1. Prove theorem 3(b) using the truth table method. SPST switches may be wired to aid you in understanding the theorem. Record the Proof and draw the equivalent circuit.

- 2. Prove theorem 6(b) and draw the equivalent circuit. Record your results.

- 3. Construct the experimental circuit in figure 2-10.

Fig. 2-11 Experimental Switching Circuit

- 4. Write the Boolean expression for the experimental circuit.

- 5. Using a truth table, verify the output of the experimental circuit in figure 2-6.

- 6. Simplify the expression using the theorems and construct the equivalent circuit. Record the steps in the mathematical simplification and draw the simplified circuit.

- 7. Verify that the simplified circuit produces the same output as the experimental circuit in figure 2-10. Record the truth table.

- 8. Construct the switch circuit as shown in figure 2-11.

- 9. Write the Boolean equation for this circuit. Record it in the data table.

- 10. Develop a truth table for this experimental circuit and record your results.

- 11. Simplify the circuit as much as you can mathematically and verify your results by the truth table. Draw the simplified circuit.

- Using single-pole-double-throw switches, construct a circuit and make a truth table for Theorem 8. Record your circuit diagram and truth table results.

ANALYSIS GUIDE. In analyzing the data from this experiment, you should compare the Boolean algebra method of circuit description with the hardwire approach. Do they agree? Which method is easier? Why?

#### PROBLEMS

- 1. Simplify (AB + A) C = output

- 2. Draw the circuit diagram for the following expression. Do not simplify.

wx + wz + wy + x'y'

3. Check the identity of each of the following expressions with a truth table.

(a) A + A' = 1 (b)  $A \cdot A' = 0$  (c) (A') = A

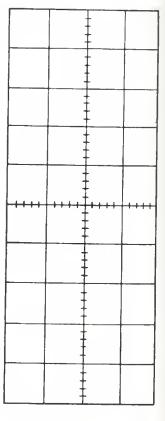

| THEOREM 3(b) | $A \times 0 = 0$ |                  |

|--------------|------------------|------------------|

|              | А                | $A \times 0 = 0$ |

|              | 1                | X =              |

|              | 0                | X =              |

|                 | THEORE | EM 6(b) |   | (A X B) + (A X | C) = / | $A \times (E$ | 3 + C) |   |

|-----------------|--------|---------|---|----------------|--------|---------------|--------|---|

|                 | А      | В       | С | (A X B) + (A X | C) = / | 4 X (E        | 3 + C) |   |

| \ /[            |        |         |   | X + X          | . =    | Х             | +      | = |

| $  \rangle / [$ |        |         |   | X + X          | =      | Х             | +      | = |

| $  \rangle    $ |        |         |   | X + X          | =      | Х             | +      | = |

| IXL             |        |         |   | X + X          |        | Х             | +      | = |

| /               |        |         |   | X + X          | =      | Х             | +      | = |

| /               |        |         |   | X + X          | =      | Х             | +      | = |

|                 |        |         |   | X + X          |        | Х             | +      | = |

|                 |        |         |   | X + X          | =      | Х             | +      | = |

|               | TRUTH | TABLE F | OR Fig. 2-10 | BOOLEAN EXPRESSION Fig. 2-10 |

|---------------|-------|---------|--------------|------------------------------|

| $\Lambda$     | А     | В       |              |                              |

| $  \rangle /$ | 0     | 0       |              |                              |

| ΙX            | 0     | 1       |              |                              |

| $ /\rangle$   | 1     | 0       |              |                              |

|               | 1     | 1       |              |                              |

| Fig. 2-10<br>SIMPLIFIED EXPRESSION | Simplified Circuit |

|------------------------------------|--------------------|

| A B                                |                    |

| X                                  |                    |

|                                    |                    |

#### Fig. 2-12 The Data Tables

# EXPERIMENT 00010 BOOLEAN ALGEBRA

| DOU 5 | Fig. 2-11<br>AN EQU |        |           |

|-------|---------------------|--------|-----------|

|       | B                   | C      |           |

| A     | D                   | C      |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

| -     |                     |        |           |

| SIMPL | IFIED EC            | UATION | Fig. 2-11 |

|       | 111-2               |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|       |                     |        |           |

|     | THEO            | REM 8 |

|-----|-----------------|-------|

| BOO | LEAN EXPRESSION |       |

| А   |                 |       |

| 1   |                 |       |

| 0   |                 |       |

|     |                 |       |

|     |                 |       |

|     |                 |       |

Fig. 2-12 The Data Tables (Cont.)

### experiment OO011 OSCILLOSCOPE WAVEFORM MEASUREMENTS

**INTRODUCTION.** The most important tool for waveform analysis is the oscilloscope. In this experiment we will set up an oscilloscope and make some measurements of waveform voltage.

**DISCUSSION.** An oscilloscope is really little more than a special kind of voltmeter. Instead of a meter movement with a pointer, it has a cathode ray tube (CRT) with an electron beam. The deflection elements cause the beam to deflect in much the same way a voltmeter deflects its pointer. The deflection in both cases is proportional to the voltage applied.

Another special feature of the oscilloscope is the fact that the electron beam is able to follow very rapid changes in the applied voltage. By thinking of the oscilloscope spot as the end of the voltmeter pointer, we can visualize the trace as a two-dimensional display of the horizontal and vertical voltages applied to the oscilloscope deflection circuits. In less expensive oscilloscopes these two inputs (horizontal and 'vertical) are often the only ones available (sometimes the cathode of the CRT is also accessible for intensity modulation of the trace.) The more expensive laboratory models have these plus many other features.

A laboratory-type instrument is often the only suitable tool for any serious wave analysis. Most of these units have DC inputs, calibrated vertical attenuators, horizontal time bases and trigger circuits, to name a few items. Among the things they will measure are: DC voltage, AC amplitude, pulse duration, frequency, period, rise time, phase, and wave shape.

The subject of this laboratory exercise covers the measurement aspects that will be primarily useful in waveform analysis. Since no single exercise can cover all the uses of this highly versatile instrument, we will confine our consideration to the ones most necessary for analyzing a wave shape.

What are the parameters which are important when considering waveforms? AC amplitude and DC level are probably the first considerations but period and frequency are also very important. The shape with regard to the rise time, duration, and polarity can be determined to establish the type of wave. These are only the most obvious considerations but they do provide us with a starting place.

In order to save time and reduce wasted effort, a technician often adopts a more-or-less standard oscilloscope setup procedure. The following is suggested as a general pattern and will require minor modification for special instruments.

- 1. Turn power switch to off.

- 2. If appropriate, plug in the desired plug-in unit.

- 3. Set the intensity, focus, gain and sync controls to their lowest settings.

- 4. Set the internal time base (sweep) generator to its calibrated position.

- 5. Set the sweep selector switch to the off or external position.

- Set the horizontal and vertical position controls to their mid-range positions.

- 7. Check the power line plug to insure that it is properly plugged in.

- 8. Turn the **power switch** to the on position.

- 9. Allow approximately one minute warm-up time before making AC measurements and five minutes before making DC measurements.

- 10. Carefully advance the intensity control until the spot appears on the screen. The lowest intensity setting that produces a clearly visible spot should normally be used to avoid damaging the CRT screen.

In the event that no spot appears with a maximum setting of the intensity control, it is probably because the spot has been deflected off the screen. Resetting the horizontal and vertical position controls should produce the spot. ONCE MORE, the intensity should be turned down before repositioning the deflection controls to avoid damaging the screen with the electron beam.

- 11. Adjust the **focus** control for a sharp, well-defined spot.

- 12. Turn up the screen illumination control and adjust it to the desired brightness.

- 13. Adjust the positioning controls for proper positioning of the spot. It should be at the left center of the screen.

- 14. For triggered sweep oscilloscopes, set the trigger mode control to the automatic position. Set the trigger slope control to the positive position. (Instruments without triggered sweep should be set to internal sweep.)

- 15. Set the sweep magnifier to X1 position and the horizontal display selector to normal sweep.

- 16. Reposition the trace so that it starts at the left edge of the screen grad-uation.

- 17. Make any necessary focus, astigmatism and intensity adjustments to obtain an easily visible line.

- 18. When using an oscilloscope with a built-in calibrator, the probe should be checked for correct compensation and calibration (including calibration of the vertical amplifiers, which is usually in the plug-in unit).

- 19. Note the type of probe to be used, X10, X1, X100, etc.

- 20. Set the vertical amp. attenuator to the one volt/cm position.

- 21. Set the square wave **calibrator** for one volt output. (Watch out for the volts, millivolt selector.)

- 22. Adjust the sweep (variable time base) for approximately one cycle for every two cm of horizontal deflection.

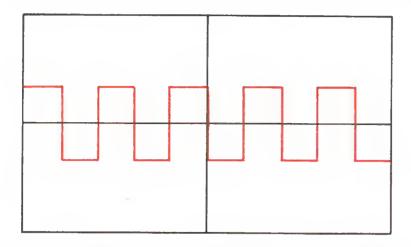

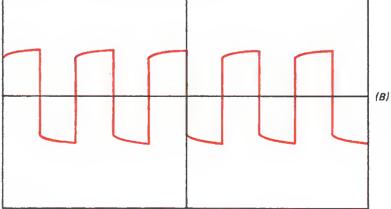

- 23. Position the waveform for convenient viewing. The amplitude of the square wave should be exactly one cm with no overshoot on the waveform leading edges. Figure 3-1 shows the proper wave-form appearance.

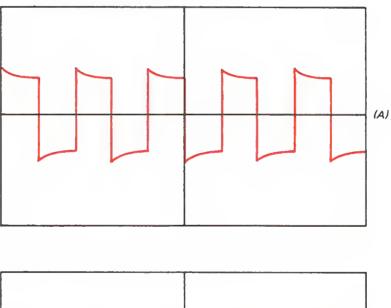

- 24. In the event that overshoot or undershoot (positive or negative sloping waveform tops) occurs, adjustment of the probe compensation may be required. Improper probe compensation is illustrated in figure 3-2.

- 25. With the probe ungrounded, touching the tip with your finger should produce a variation in the trace amplitude dominated by 60 Hz hum. If the probe is grounded with the controls set as described, a clean horizontal line should appear. It is sometimes convenient to set this line on the zero axis (center-line) of the screen. This gives the waveform a zero reference.

Fig. 3-1 Properly Displayed Square Wave One Volt Calibration – Probe Properly Adjusted

Fig. 3-2 (A) Overcompensated Probe (B) Undercompensated Probe

The foregoing steps are somewhat lengthy to list and read, but, in fact, take little time to actually perform. They may have to be modified to fit the particular instrument you will be using. You should practice setting up your scope until you can do it quickly without directions.

After the setup steps are completed, the oscilloscope is ready to accept an input signal for measurement. With most instruments the normal signal to be measured is applied to the vertical amplifier. The voltage of the input signal produces a corresponding vertical deflection of the CRT trace. In laboratory instruments the vertical amplifier is provided with calibrated attenuators for precise amplitude measurement (in most cases, By counting the voltage measurement). graduations on the face of the CRT and applying the multiplication factor to the input attenuator (Don't forget the probe attenuation), the voltage of any part of the wave shape can be determined.

Another useful measurement is that of the frequency of the wave. Using a laboratory instrument with a calibrated horizontal time base, the period of any part of the particular wave shape can be found.

All frequency measurements with the oscilloscope are based on time measurements. This is achieved by comparing the incoming wave period to the internal sweep time of the instrument. Some oscilloscopes have a time base generator which is controlled by a front panel knob calibrated in frequency units. In this case the time base is such that the periodto-frequency calibrations are automatic.

In any oscilloscope, if the time period for one complete cycle can be determined, the frequency can be calculated. This is possible since frequency is the reciprocal of the time duration. In pulse or digital work, an instrument with a calibrated sweep control is most desirable. For that reason this discussion will be limited to this type of oscilloscope.

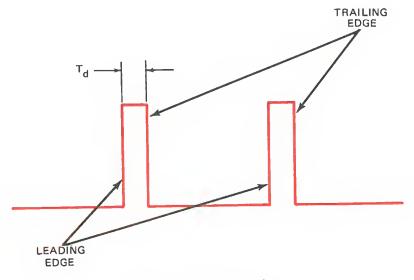

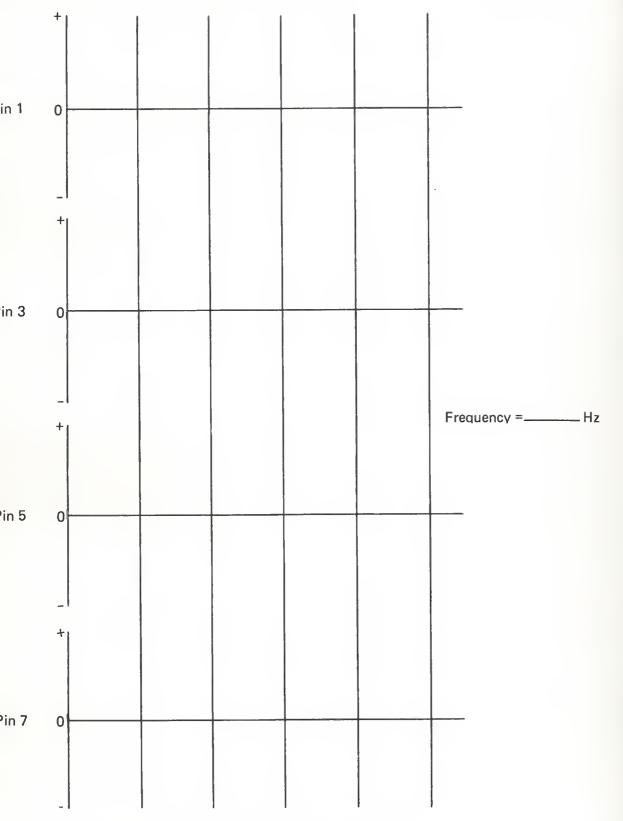

First we will consider how to measure duration. This measurement becomes important in digital work for determining the width and frequency (pulse repetition rate or frequency.) It is convenient to use the following steps in making time measurements.

- 1. Place the oscilloscope in operation according to your setup procedure.

- Set the vertical attenuator to a deflection factor which will display the expected signal without overdriving the vertical amplifier.

- Apply the signal to be measured to the vertical input.

- Set the sweep trigger slope and mode to Internal, + and Automatic, respectively.

- 5. Adjust the sweep rate (time/cm) until a convenient number of divisions between the points on the waveform to be measured can be viewed. Due to nonlinearity at the beginning and end of the sweep, it is recommended that the extreme edges of the screen not be used. Normally, the fastest reasonable sweep rate will be best for easy calculations.

- The horizontal and vertical position controls may be used to position the waveform as needed for measurement.

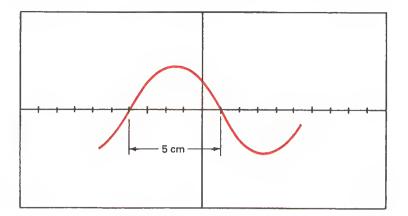

- Count the number of centimeters between the points on the waveform to be measured (figure 3-3). Make sure the sweep variable control is in the calibrated position before taking the reading.

- The time duration between the two points can be determined by equation 3.1.

Fig. 3-3 Time Duration

Time Duration =  $\frac{\text{horizontal distance (cm) } \times \text{ horizontal sweep setting}}{\text{magnification}}$  (3.1)

For example: Horizontal distance = 5 cm (figure 3-3) Horizontal sweep speed = 0.1 ms/cm Sweep normal (magnification X 1)

Substituting in 3.1,

$TD = \frac{5 \times 0.1}{1} = 0.5$  milliseconds

Once the time duration is found, only one more calculation is required to obtain frequency.

Frequency =

$$\frac{1}{\text{Time Duration}}$$

(3.2)

To continue the example,

$$f = \frac{1}{0.5 \text{ ms}} = 2000 \text{ Hz}$$

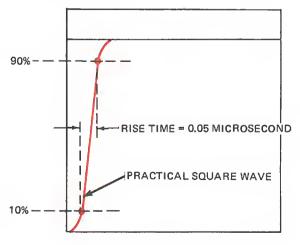

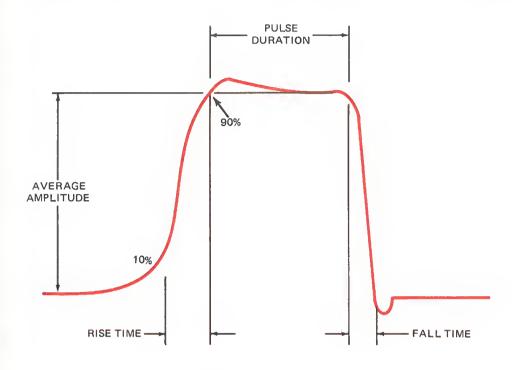

This procedure covers the major considerations for measuring time duration and frequency. One other major measurement should be considered in order to have a good foundation for pulse and digital work. This last measurement we wish to consider is that of rise time. In theory, square wave and pulses are perfectly square and have instantaneous rise times. In practice, however, a finite amount of time is required for the voltage to rise to the top of the waveform. Simply, then, the rise time could be considered the time required for the voltage to reach its maximum. To eliminate the corners and to give a more constant value, *rise time is defined as the time required for the voltage to rise from* 10% to 90% of its total excursion. Rise time is shown in figure 3-4.

Fig. 3-4 Rise Time

With a good scope that has a calibrated sweep, rise time can be easily measured. It can be read directly from the screen using the method discussed for time duration measurements. The only difference is in the positioning of the waveform so as to be able to read the time duration between the 10% and 90% points.

There are a few points relative to rise time measurements that are worth remembering. The instrument used to measure rise time must have considerably better characteristics than the unit under test. That is, if a scope is being used to check the rise time of a signal generator, the scope must have a much faster rise time than the generator.

As a rough measure, the rise time of an amplifier is about 1/3 of the period at the high frequency cutoff. This says that a scope with a pass band of 4 Hz has a rise time in the vicinity of 0.08  $\mu$ s. Four megahertz have a period of 0.25 microseconds; therefore, the rise time of a four megahertz scope is about

$1/3 \times 0.25 \ \mu s$  or 0.08 microseconds

#### MATERIALS

- 1 Oscilloscope with probe

- 1 DC power supply (0-40V)

1 Function generator 1 VOM or FEM

#### PROCEDURE

- 1. Set up the scope using the procedure outlined in the discussion.

- 2. Calibrate the probe using the procedure outlined in the discussion.

- 3. Set the DC power supply to approximately 10 volts.

- 4. Measure the DC voltage with the oscilloscope and with the multimeter.

- 5. Repeat steps three and four for one volt differentials to 15 volts.

- 6. Apply a IV peak to peak 100 Hz sine wave to the oscilloscope vertical amplifier.

- 7. Read the amplitude of the signal with the scope and with the multimeter.

- 8. Repeat steps 6 and 7 in IV steps up to five volts.

- 9. Apply a 30 Hz sine wave to the scope input.

- 10. Read and record the time duration of one-half cycle.

- 11. Repeat steps 9 and 10 for 60, 100, 200, 500, 1000 Hz.

- 12. Determine the frequency of each wave using your period measurements.

- 13. Apply a 100 Hz pulse or square wave to the scope.

- 14. Determine the rise time of the signal.

- 15. Repeat 13 and 14 for 500 Hz and 1 kHz.

ANALYSIS GUIDE. In analyzing these data you should compare the accuracy obtained using the oscilloscope to that obtained with the multimeter for AC and DC voltage measurement. Discuss the reasoning behind the use of a calibrated horizontal sweep as a basis for measuring period and frequency.

| DC Volts                             | 10 | 11 | 12 | 13 | 14 | 15 |

|--------------------------------------|----|----|----|----|----|----|

| Power Supply Reading<br>(Multimeter) |    |    |    |    |    |    |

| Oscilloscope Reading                 |    |    |    |    |    |    |

| Audio Generator Hz      | 30 | 60 | 100 | 200 | 500 | 1000 |

|-------------------------|----|----|-----|-----|-----|------|

| Time Duration 1/2 Cycle |    |    |     |     |     |      |

| Frequency               |    |    |     |     |     |      |

| AC Volts             | 1 | 2 | 3 | 4 | 5 |

|----------------------|---|---|---|---|---|

| Multimeter Reading   |   |   |   |   |   |

| Oscilloscope Reading |   |   |   |   |   |

| Frequency | 100 Hz | 500 Hz | 1 kHz |

|-----------|--------|--------|-------|

| Rise Time |        |        |       |

#### Fig. 3-5 The Data Tables

#### PROBLEMS

- 1. Why is it necessary to have a faster rise time on the scope used to make the measurement than the instrument under test? If this is not so, what does the rise time measured correspond to?

- 2. What is the period of a 1 kHz waveform?

- 3. A certain waveform has a horizontal deflection of 8 cm for one complete cycle. The horizontal sweep control is set to 0.1 millisecond/cm. The sweep magnification is off. What is the time duration of the entire cycle? What is the frequency of the waveform?

# experiment OO100 BASIC WAVEFORMS

**INTRODUCTION.** Waveforms are used in logic circuits to transmit information to the individual logic devices. In this experiment some of the basic waveforms will be examined and their characteristics considered.

DISCUSSION. Logic devices are of tremendous importance to us. The complex computers of this age allow us to travel in space as well as to do our ordinary household chores. These devices are usually thought of as being largely electronic, and it is true that electronics plays a major role. However, it is a mistake to believe that all logic is electronic. Logic, like all basic principles, spans the realm of physical science and even enters the area of philosophy and the mind in human encounter. Logic is a tool used by the first and most basic computer, the human mind.

For our purposes we can narrow the application to some specific areas of the physical sciences. These areas are electronics, mechanics, hydraulics and pneumatics. It is true that most of the language (in fact, at the present time, the application of logic) is in the electronic field, but the past few years have seen rapid development in the nonelectronic areas of logic as well.

Logic in any physical form deals with the parameters of the field of application corresponding to voltage, current, and power transmission. These parameters are combined to produce waveforms and pulses in the medium used for the passage of information. The medium can be air, oil, water, copper, etc. Because electricity and electronics have been operating in this area, the language, methods, and techniques are well-defined. For this reason we will use electronics as the vehicle for our study, keeping in mind the fact that the principles are applicable to a variety of mediums.

Basic to the study of logic is the study of waveforms. They are used to code or tell the logic circuits what to do by changing the magnitude, shape, frequency, etc., which includes the changing of direction or level of a current or voltage.

Fortunately, highly sophisticated and very useful tools have been developed for the study of electrical waveforms. The most common of these is the cathode ray oscil-This instrument produces a dot loscope. of light which, when properly calibrated as to time and amplitude, will produce a representation of a voltage waveform on the screen of its cathode ray tube. Other devices such as the mechanical strip chart recorders are also used, but the basic principle is the same.

In most cases of interest the pattern of changes will repeat itself at a given rate. When this happens the waveform is said to be periodic. From this concept is developed the idea of frequency. Each repetitive combination is defined as a cycle. The number of times it cycles in a given time period (usually one second) is termed the frequency. The units of frequency are cycles per second and are The time taken to expressed in Hertz. produce each cycle is called the period. The units of period are seconds. The relationship

between the frequency and period of a waveform is

$$f = \frac{1}{T}$$

(4.1)

where f = frequency in Hertz T = the time in seconds for one complete cycle.

This expression will be used over and over in various forms as we examine wave analysis. It is particularly useful when an oscillosocpe is employed for wave analysis. The horizontal scale on most scopes is directly calibrated in time (or frequency) units. The period of the wave can be found by observing the time duration for one complete cycle. Taking the reciprocal of time duration (or period) will yield the frequency.

Periodic waveforms are easily displayed on a laboratory-type oscilloscope. Since the pattern is traced repeatedly, it can be positioned and measured. Normally it is good practice to use a horizontal time base that will display at least two complete cycles. If only one cycle is shown, there is a danger that inaccuracy will develop due to time lost while the electron beam in the scope is returned to its starting point.

Aperiodic waves are not readily displayed on the ordinary laboratory oscilloscope because these waves, by definition, do not occur at a cyclic rate. They must be displayed on some type of recording oscillograph. Some of these waveforms occur only when the circuit is turned on or off or when a dramatic change of state occurs. Variations of this type are called transients. Sometimes we are very interested in these because of the effect they have on circuits and devices. For the present we will be primarily concerned with periodic waveforms.

Sinusoidal variations are found throughout the physical sciences. They produce the familiar wave pattern called "sine waves" which result from graphing the trigonometric sine function. Sinusoidal waves are mentioned here as a starting point only. They are, generally speaking, of little interest in digital circuits. We will be dealing largely with nonsinusoidal waves. These waves are those of voltage or current whose changes are not sine functions.

There are two methods for analysis of nonsinusoidal waves. The first is a mathematical method in which any periodic waveform can be expressed as a combination of a DC component and a number of pure sine waves of different amplitudes, frequency and phase. The time period of the periodic nonsinusoidal wave will be a whole number multiple of the time period of each of its component sine waves. These component sine waves are called harmonics of the given frequency. The sine wave with the lowest frequency is called the fundamental. The ratio of the frequency of a harmonic to the frequency of the fundamental is the number of the harmonic. For instance, if a fundamental frequency of 200 Hz is given, the third harmonic is 600 Hz and the fifth is 1 kHz. The mathematical process by which these component waves are determined is called Fourier Analysis. Notice that the first harmonic is the same as the fundamental (200 Hz). The Fourier system has all of the advantages of a mathematical representation. Equations can be written whose graphical representation produces the amplitude spectra of the waveform.

The general trigonometric equation for a square wave is

$$e = \frac{4}{\pi} \left[ \sin \omega t + \frac{1}{3} \sin 3 \omega t + \frac{1}{5} \sin 5 \omega t + \dots + \frac{1}{(2N - 1)} \sin (2N - 1) \omega t \right]$$

(4.2)

| where | e = voltage amplitude at any        |

|-------|-------------------------------------|

|       | time t                              |

|       | N = term number                     |

|       | (2N - 1) = harmonic number which is |

|       | always odd                          |

|       | $\omega$ = angular velocity of the  |

|       | fundamental                         |

|       |                                     |

Several things can be determined by observing the general equation for a wave. From equation 4.2 we can tell that this square wave contains only odd harmonics (the 1, 3, 5, etc.). Also there is no DC component because this equation is symmetrical about the horizontal axis (the average value for e, the amplitude, is zero).

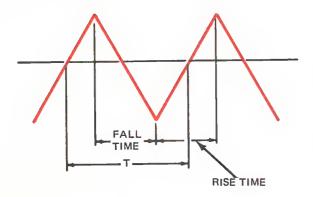

Observe the following equation for a sawtooth wave:

$$e = \frac{2}{\pi} \left[ \sin \omega t - \frac{1}{2} \sin 2 \omega t + \frac{1}{3} \sin 3 \omega t + \dots \right]$$

$$\frac{(-1)^{N}}{N} \sin N \omega t$$

(4.3)

From equation 4.3 we can determine that all the harmonics are present (odd harmonics have + signs and even harmonics have -). The wave is symmetrical about the horizontal axis.

The general equation for a rectangular pulse waveform is

ELECTRONICS/DIGITAL

$$e = \frac{\theta}{\pi} + \frac{2}{\pi} \left( \sin \omega t \cos \omega t + \frac{\sin 2 \omega t \cos 2 \omega t}{2} + \frac{\sin 3 \omega t \cos 3 \omega t}{3} + \frac{\sin 4 \omega t \cos 4 \omega t}{4} + \dots + \frac{\sin N \omega t \cos N \omega t}{N} \right)$$

(4.4)

where  $\theta = (\pi)$  (duty cycle)

All harmonics are present and a DC component is present because none of the waveforms fall below the horizontal axis. The duty cycle is the percentage of time the overall wave is at its maximum value.

All of these equations theoretically have infinitely many terms but in application, no more than 10 to 20 sine waves are required to describe a waveform. The higher-numbered harmonics become small enough to be negligible after that. Pulse waveforms may require more harmonics to be adequately represented, depending on the duty cycle. That is, the number of harmonics required is inversely proportional to the duty cycle. This rule is important for short duty cycles only.

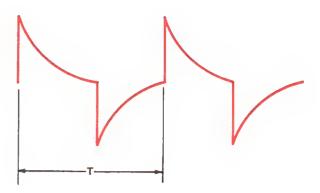

After the sine wave, which is normally covered in AC circuit courses, the most prominent basic waveform is the square wave. Let's continue our discussion of square waves using a second method of analysis. In this second method the wave is considered as variations made up of small segments. The segments themselves can be thought of as being one of four basic shapes. These shapes are the sine, step, ramp, and exponential waveforms. A truly square wave is made up of a series of step voltages. A step voltage is a sudden change from one constant voltage

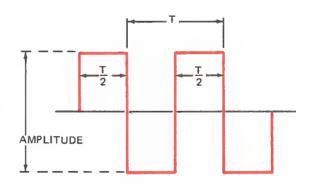

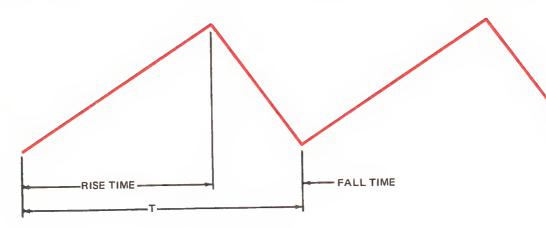

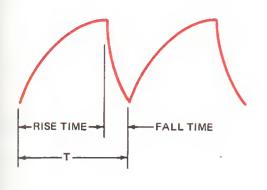

level to another. Theoretically, we like to think of this change as instantaneous. Any change does, however, require some finite length of time. This length of time is usually very short compared with the time of the preceding constant level. This sudden change can be in either the positive or negative direction from the constant level. The amplitude of the step is defined as the difference of the two constant levels. Figure 4-1 shows a square waveform.

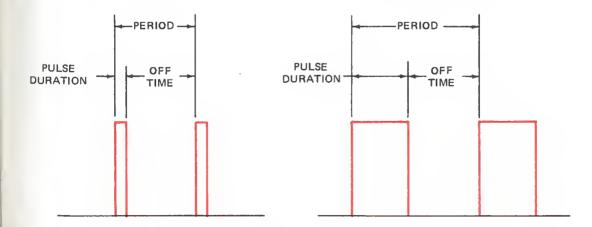

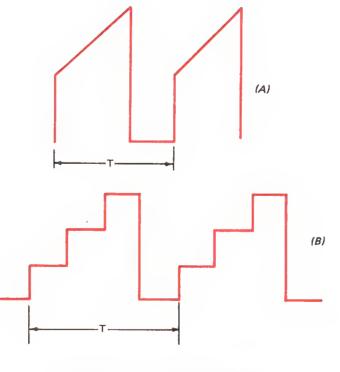

The period of the square wave is the time T in figure 4-1. A square wave has a stepped voltage (at a constant level) for a time duration which is equal to one-half the This brings up the idea of a recperiod. tangular pulse waveform. A rectangular pulse waveform is similar to a square wave in that it is also made up of step function segments. The only practical difference is in the relationship of the time duration to the period. If the square waveform is considered to be made up of square pulses which have an "on" time (when the step function suddenly moves to maximum amplitude) that is equal to the "off" time (step function drops to zero), the square wave is a special case of the general rectangular pulse wave-The duty cycle of any rectangular form.

Fig. 4-1 Square Waveform

pulse waveform can be calculated by

Duty Cycle (%) =

$$\frac{\text{Pulse "on" time}}{\text{Pulse period}} \times 100$$

(4.4)

The square wave can be described as a special type of rectangular pulse having a 50% duty cycle. When the duty cycle falls below the 50% ratio, the waveform is defined as a rectangular wave. A rectangular wave is any wave whose pulse width is less than ten times its pulse duration.

Period

$$<$$

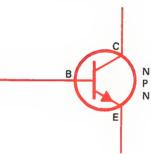

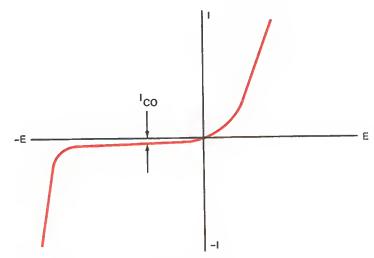

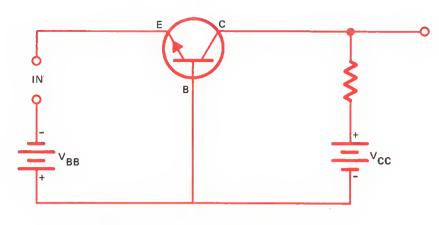

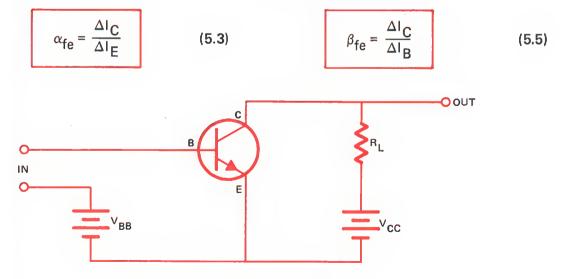

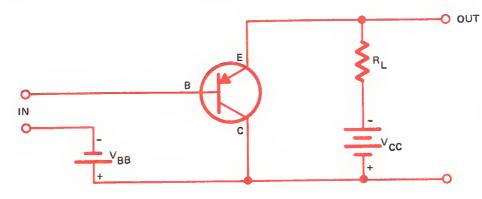

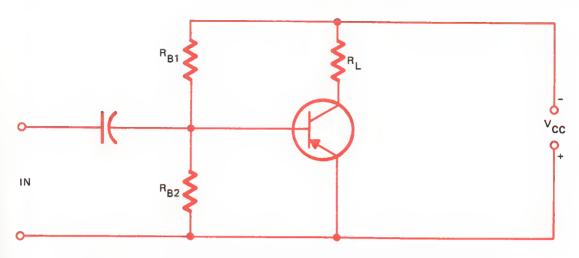

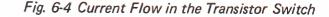

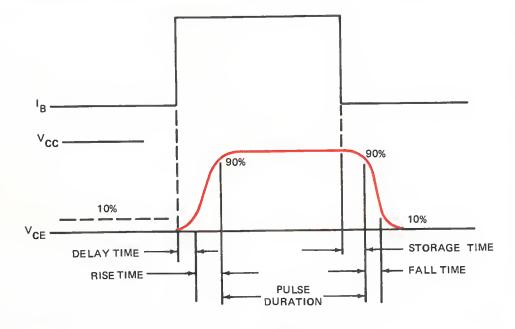

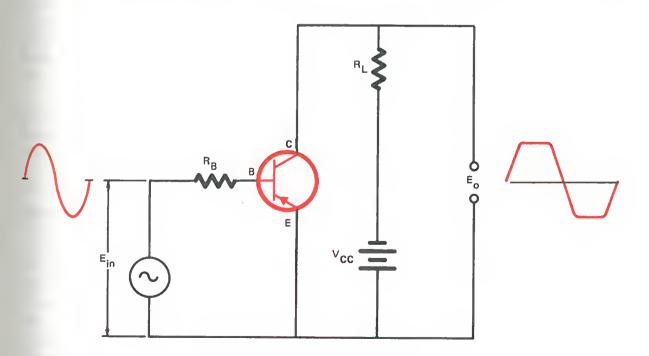

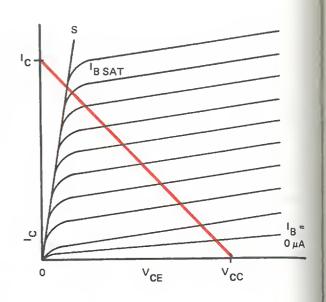

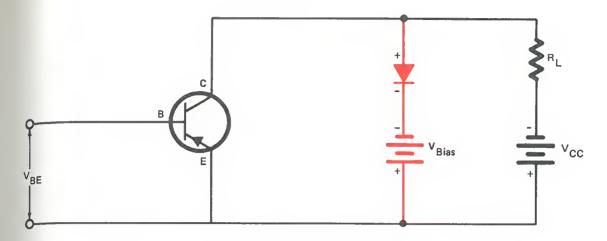

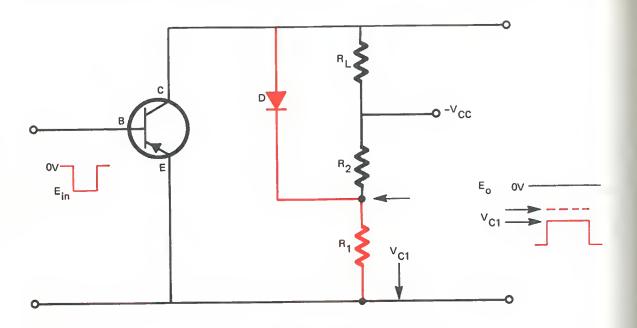

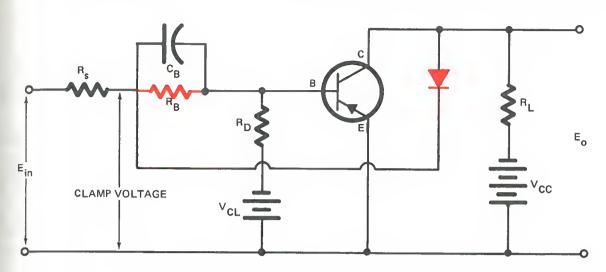

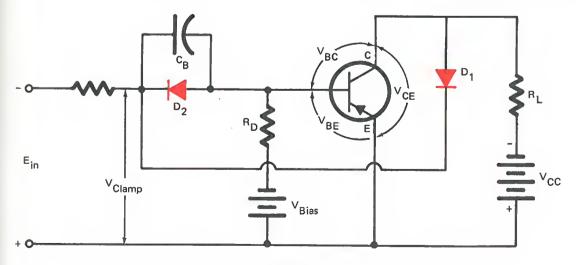

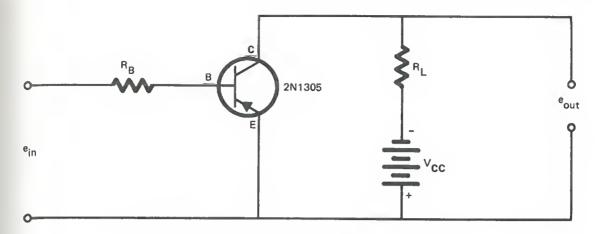

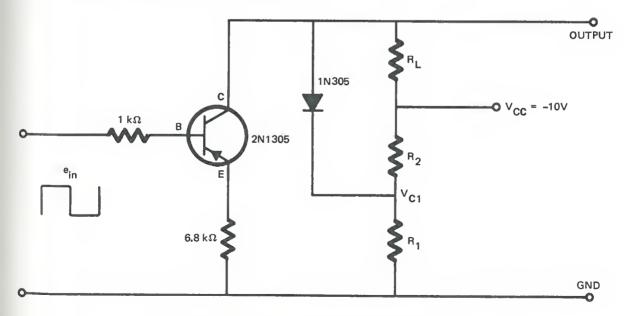

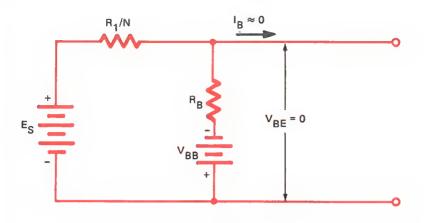

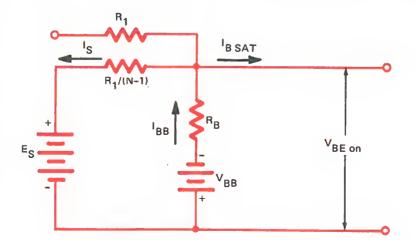

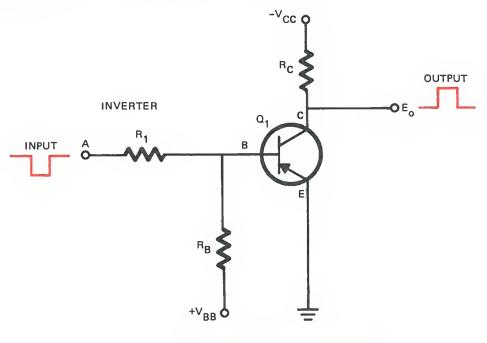

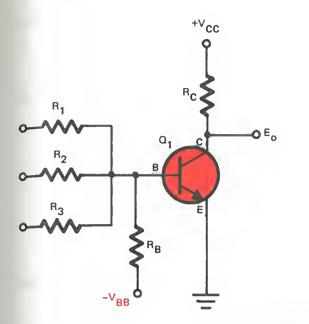

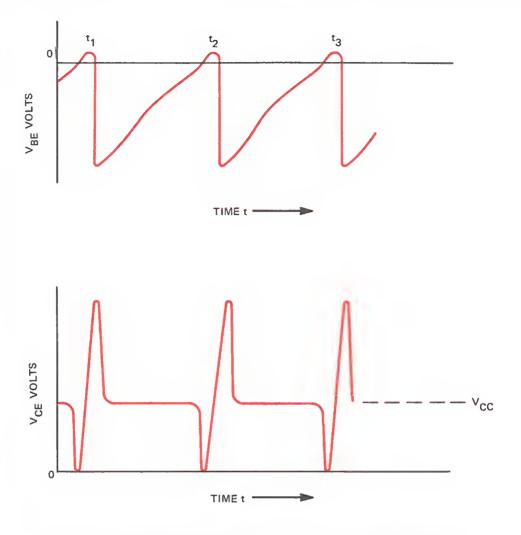

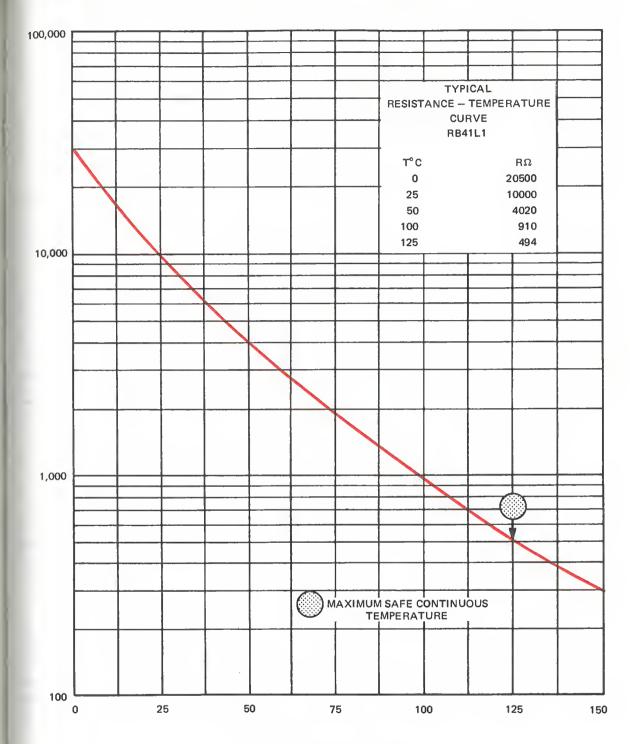

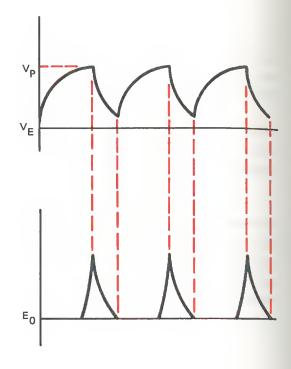

10 (pulse duration) (4.5)